#### FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

## **Inductorless DC-DC Converter**

Fábio Pascoal

FINAL VERSION

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Internal Supervisor: Vítor Grade Tavares (PhD)

External Supervisor: Joaquim Machado

## Resumo

Assim que a eletricidade se tornou um bem essencial, trouxe consigo a necessidade de conversão de energia. Os conversores CC-CC fazem parte desta classe e desempenham a tarefa de converter um sinal de tensão constante e estável, num sinal de outro nível. A forma de cumprir este objetivo mudou com o decorrer dos tempos. Anteriormente ao aparecimento dos semicondutores de potência, converter um nível de tensão constante noutro passava por primeiro converter esse sinal num sinal AC, converter o seu nível com um transformador e retificar a onda para obter novamente um sinal CC. Até aos dias de hoje continua-se a investigar nesta área porque os desafios assim o exigem e as ferramentas tecnológicas, mais poderosas, também assim o permitem. Os conversores CC-CC são usados em dispositivos portáteis, alimentados a bateria, que podem conter em si subsistemas a operar com diferentes níveis de tensão, sendo também commumente utilizados em sistemas de captação de energia.

O uso de indutores sempre foi uma componente forte na construção de conversores CC-CC, no entanto, a dado momento surgiram alternativas usando apenas condensadores. O principio de funcionamento passa sempre por armazenar energia em componentes eletrónicos capazes disso, como é o caso do indutor e do condensador, e comuta-los através de dispositivos semicondutores, libertando a energia armazenada a um nível de tensão diferente. Mas quando se fala de circuitos integrados, o indutor torna-se pouco desejável pois é origem de interferência eletromagnética, é caro, espaçoso, mas acima de tudo, difícil de integrar. A alternativa aos indutores passa por usar o *Charge Pump*, um tipo de circuito de condensadores comutados que permite obter uma tensão a um nível diferente da alimentação, abdicando do uso de indutores.

Este trabalho apresenta um circuito *Charge Pump* que cumpre determinados objetivos de desempenho e que é projetado para suportar variações de alimentação, de processo e temperatura. As especificações que serão almejadas são, nomeadamente: a tensão de entrada e sua variação admitida e tensão de saída e variação tolerada. Utiliza *Charge Pumps* auxiliares para implementar técnicas de *gate-boostrapping* para elevar o sinal de comando da comutação acima da alimentação, diminuindo a resistência dos interruptores, causando menos perdas e permitindo aumentar a frequência o que poupa no tamanho dos condensadores. Para regular a saída apresenta-se uma proposta de *Pulse-Skipping*, juntamente com PWM, que pode ser realizada com comparadores e lógica simples. Este trabalho é realizado em ambiente empresarial, na Synopsys - Portugal.

## **Abstract**

DC-DC converters are an area of interest since electricity emerged as a common utility. They perform the task of converting a constant and stable voltage signal into another of different level. The way to achieve this goal has changed over time. Before power semiconductors were available, converting a constant level of voltage into another would demand converting the DC voltage into AC first, then the amplitude adjusted with the help of a transformer followed by a rectifier, that would recover the DC voltage to a different level. Even today, investigation still continues on these matters, because the challenges so requires and technological tools, more powerful, also allows it. DC-DC converters are used in portable devices that are battery powered, which can contain in themselves subsystems operating at different voltage levels, and are also commonly used in energy harvesting systems.

The use of inductors has always been a strong component in the construction of DC-DC converters, however, alternatives have emerged using solely capacitors. The operating principle always consists in storing energy in electronic components capable of such, as it is the case of the inductor and capacitor, and switching them through semiconductor devices, releasing the stored energy at a different voltage level. But when it comes to integrated circuits, the inductor becomes undesirable as it is a source of electromagnetic interference, it is expensive, spacious but above all, difficult to integrate. Charge Pumps have become a viable alternative to the use of inductors, a type of switched capacitor circuit that enables a voltage conversion avoiding the use of inductors.

This work presents a Charge Pump circuit that meets certain performance goals and is designed to support changes in process, voltage and temperature. Auxiliary Charge Pumps implement gate-boostrapping techniques that raises the switching command voltage above the power supply, in order to reduce the equivalent resistance of the switches, causing lower losses, allowing increased frequency operation, thus saving capacitor size. To adjust the output a Pulse-Skipping Control is proposed along with PWM control, which can be realized with comparators and simple logic. This work is carried out in a business environment, more specifically at Synopsys - Portugal.

## Acknowledgements

Firstly I thank my parents for supporting me in all my academic and non-academic decisions. Also I am very thankful for the sacrifices they made throughout the years in order for me to have a good education.

To my girlfriend that supported me for most my university years and for her understanding towards my reduced availability during the elaboration of this thesis.

To all my friends at FEUP that shared with me these five years of friendship, study and laughs.

To the analogue team at Synopsys for the support with the complex tools, the good work environment, the afternoon snacks and above all for the constant reminder of having a Thesis to do.

To my supervisors Joaquim Machado and Prof. Vítor Grade Tavares for allays finding time, in their busy schedules, for me and contributing with very valuable ideas for this work.

Fábio Pascoal

"Study hard what interests you the most in the most undisciplined, irreverent and original manner possible."

Richard Feynman

# **Contents**

| Re | Resumo |                                                           |    |  |  |  |  |  |

|----|--------|-----------------------------------------------------------|----|--|--|--|--|--|

| 1  | Intr   | oduction                                                  | 1  |  |  |  |  |  |

|    | 1.1    | Motivation                                                | 1  |  |  |  |  |  |

|    | 1.2    |                                                           | 2  |  |  |  |  |  |

|    | 1.3    | Objectives                                                | 2  |  |  |  |  |  |

|    | 1.4    | Dissertation Structure                                    | 2  |  |  |  |  |  |

| 2  | Bac    | Background and Bibliographical Review 5                   |    |  |  |  |  |  |

|    | 2.1    | DC-DC converters                                          | 5  |  |  |  |  |  |

|    | 2.2    | Cockcroft-Walton Charge Pump                              | 6  |  |  |  |  |  |

|    | 2.3    | Dickson Charge Pump                                       | 9  |  |  |  |  |  |

|    | 2.4    | CTS based Charge pumps                                    | 0  |  |  |  |  |  |

|    | 2.5    | Modern Charge Pumps                                       | 2  |  |  |  |  |  |

|    |        | 2.5.1 Summary                                             | 4  |  |  |  |  |  |

| 3  | Cha    | Charge Pump Design 15                                     |    |  |  |  |  |  |

|    | 3.1    | Performance Goals                                         | 5  |  |  |  |  |  |

|    | 3.2    | Operation with variation of PVT                           | 5  |  |  |  |  |  |

|    | 3.3    | Charge Pump Topology                                      | 6  |  |  |  |  |  |

|    |        | 3.3.1 Basic operation of a Charge Pump                    | 7  |  |  |  |  |  |

|    |        | 3.3.2 Dynamic CTS Charge Pump: Advantages and limitations | 5  |  |  |  |  |  |

|    |        | 3.3.3 Choice of Topology                                  | 6  |  |  |  |  |  |

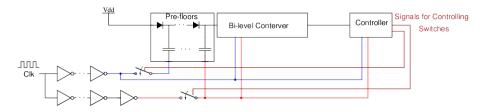

|    | 3.4    | Bi-level Converter                                        |    |  |  |  |  |  |

|    |        | 3.4.1 General Operation                                   | 7  |  |  |  |  |  |

|    |        | 3.4.2 Choice of bi-level converter                        | 7  |  |  |  |  |  |

|    | 3.5    | Parameter Definition and Optimization                     | 7  |  |  |  |  |  |

|    | 3.6    | Closed-Loop Regulation                                    | 0  |  |  |  |  |  |

|    |        | 2 7                                                       | 0  |  |  |  |  |  |

|    |        | 3.6.2 Regulation of the Output                            | 2  |  |  |  |  |  |

|    | 3.7    | Summary                                                   | .7 |  |  |  |  |  |

| 4  | Fina   | Final Circuit Proposal and Results 49                     |    |  |  |  |  |  |

|    | 4.1    | •                                                         |    |  |  |  |  |  |

|    | 4.2    | Simulations and Results                                   |    |  |  |  |  |  |

|    |        |                                                           | 0  |  |  |  |  |  |

|    |        |                                                           | 0  |  |  |  |  |  |

|    |        |                                                           | 3  |  |  |  |  |  |

X CONTENTS

|            |      | 4.2.4    | Irregular Loads simulation      |  | . 55      |

|------------|------|----------|---------------------------------|--|-----------|

|            |      | 4.2.5    | Maximum Rating                  |  | . 57      |

|            |      | 4.2.6    | Monte Carlo                     |  | . 58      |

|            | 4.3  | Summ     | ary                             |  | . 59      |

| 5          | Con  | clusions | s and Future Work               |  | 61        |

|            | 5.1  | Work I   | Development Summary             |  | . 61      |

|            | 5.2  | Goal e   | evaluation                      |  | . 63      |

|            | 5.3  | Future   | e Work                          |  | . 63      |

| Αŗ         | pend | ices     |                                 |  | 65        |

| A          | App  | endix A  |                                 |  | <b>67</b> |

|            | A.1  | Results  | s of Irregular Load Simulations |  | . 67      |

| References |      |          |                                 |  | 73        |

# **List of Figures**

| 2.1  | DC-DC converter using an inductor                                                  |

|------|------------------------------------------------------------------------------------|

| 2.2  | Cockcroft-Walton Charge pump, taken from [1]                                       |

| 2.3  | Double Cockcroft-Walton Charge Pump                                                |

| 2.4  | Phase 1 of the operation of the Cockcroft-Walton converter                         |

| 2.5  | Phase 2 of the operation of the Cockcroft-Walton converter                         |

| 2.6  | Dickson Charge Pump with stray capacities, taken from [2]                          |

| 2.7  | Cockcroft-Walton Charge Pump with stray capacities, taken from [2]                 |

| 2.8  | Cockcroft-Walton Charge Pump with stray capacities, taken from [2] 10              |

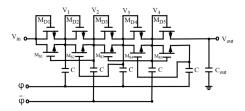

| 2.9  | Static CTS based Charge Pump, taken from [3]                                       |

| 2.10 | Dynamic CTS based Charge Pump, taken from [3]                                      |

| 2.11 | Dynamic CTS based Charge Pump, taken from [3]                                      |

| 2.12 | Modern Charge Pump, taken from [4]                                                 |

| 2.14 | Switch proposed, taken from [5]                                                    |

| 2.13 | Series-Parallel Trippler, taken from [5]                                           |

| 3.1  | Commutating the source with an inverter                                            |

| 3.2  | Opposite phase signal to switch the source                                         |

| 3.3  | Switch based Charge Pump Topology                                                  |

| 3.4  | Equivalent Circuit during discharge phase                                          |

| 3.5  | Equivalent Circuit during charge phase                                             |

| 3.6  | Voltage waveform during discharge phase                                            |

| 3.7  | Turning on a NMOS switch                                                           |

| 3.8  | Turning off a NMOS switch                                                          |

| 3.9  | Two-stage Dynamic CTS Charge Pump                                                  |

|      | Proto-bi-level                                                                     |

| 3.11 | Proto-bi-level converter of Dynamic CTS charge pump                                |

| 3.13 | Wave aspect for each stage in Bi-level converter (First stage in brown, second     |

|      | stage in blue and third stage in red)                                              |

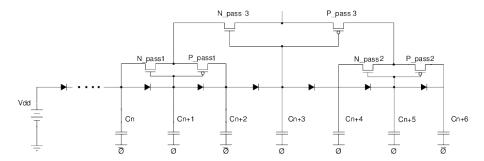

| 3.12 | N-stages Singular Bi-level Converter                                               |

| 3.14 | Aspect of circuit part responsible for charging the output                         |

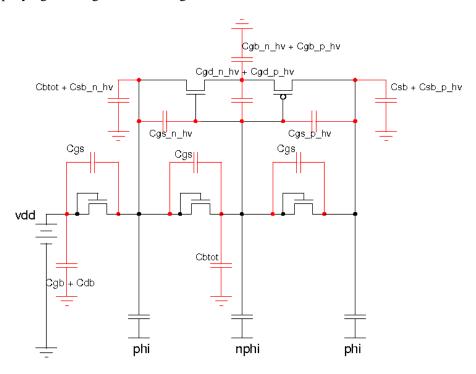

| 3.15 | Single-Floor Bi-level converter with all the transistors' stray caps represented 3 |

| 3.16 | Single-Floor Bi-level converter with all the equivalent stray capacitances of the  |

|      | transistors represented                                                            |

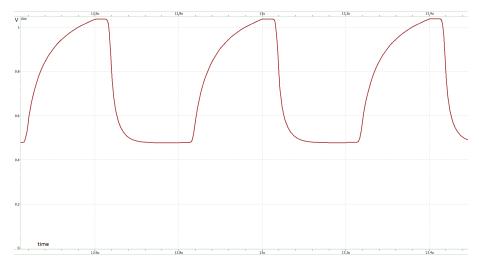

| 3.17 | Waveform of the output of a Bi-level converter with pull-up problems               |

| 3.18 | Waveform of the output of a Bi-level converter with pull-down problems 33          |

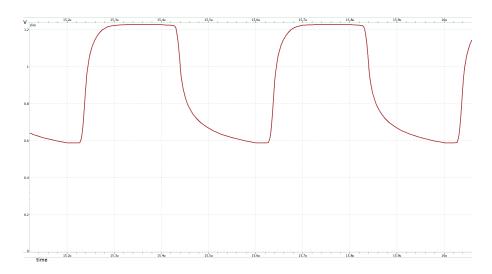

| 3.19 | Two-stage Dynamic CTS Charge Pump                                                  |

| 3.20 | Waveform of the output of a two-stage dynamic CTS Charge Pumps                     |

xii LIST OF FIGURES

| 3.21 | nificant load.                                                                              |

|------|---------------------------------------------------------------------------------------------|

| 3 22 | Intermediate floor Bi-level converter with pre-added stages                                 |

|      |                                                                                             |

| 3.23 | Maximum output voltage of a bi-level converter for different internal capacitances          |

| 2 24 | in function of period                                                                       |

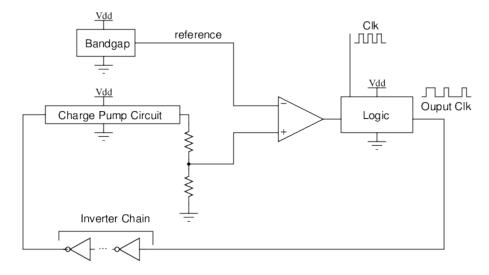

|      | Regulation scheme of a Charge Pump                                                          |

|      | Regulation scheme of a Bi-level converter                                                   |

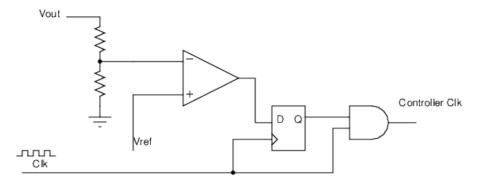

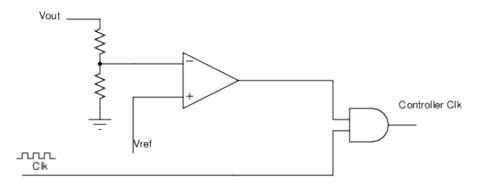

| 3.26 | Pulse-Skipping Controller Diagram.                                                          |

|      | Pulse-Width Controller Diagram.                                                             |

|      | High Boost - Low Current case with PWM control                                              |

|      | High Boost - High Current case with PWM control                                             |

|      | Low Boost - Low Current case with Pulse-Skipping Control control                            |

|      | High Boost - High Current case with Pulse-Skipping and PWM Control control                  |

|      | Low current cases with Pulse-Skipping and PWM Control control                               |

| 3.33 | Pulse-Skipping and PWM Controller Diagram                                                   |

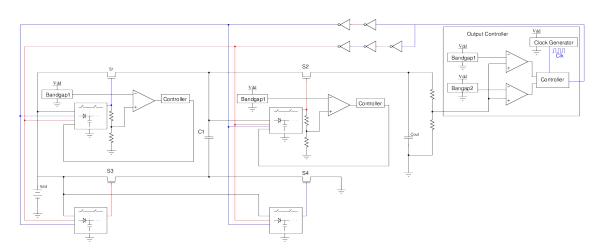

| 4.1  | Diagram of the proposed circuit                                                             |

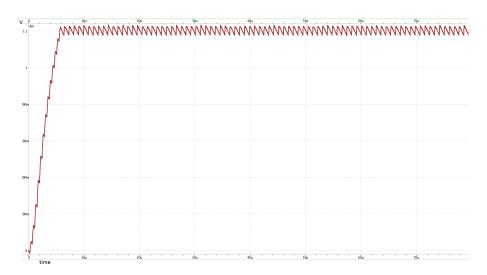

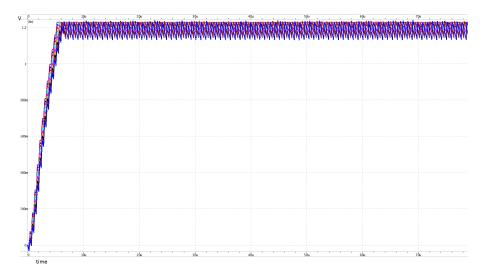

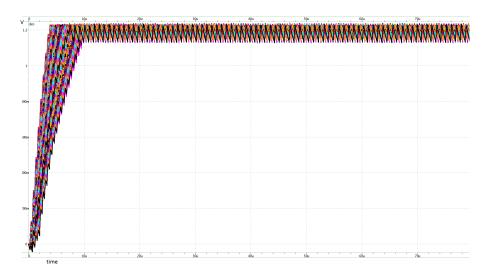

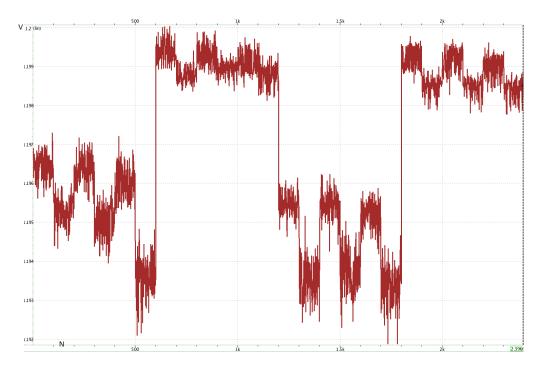

| 4.2  | Output voltage waveform for the typical case, supplying 10mA                                |

| 4.3  | Output voltage waveform for various input voltages                                          |

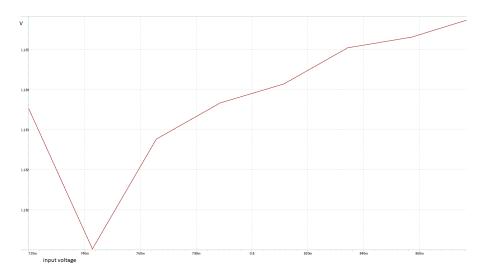

| 4.4  | Output voltage waveform for various input voltages                                          |

| 4.5  | Output voltage waveform for various input voltages at various PVT corners                   |

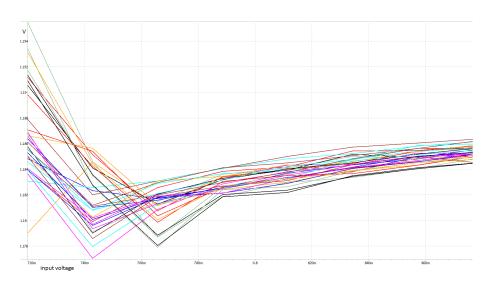

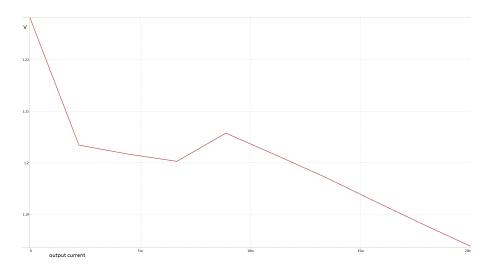

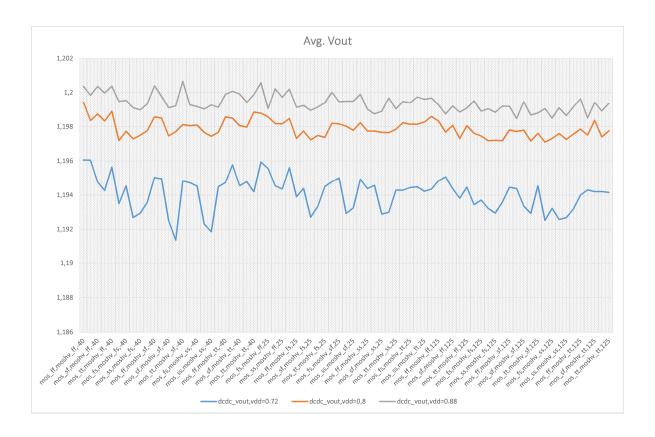

| 4.6  | Average Output voltage as a function of input voltage for each corner                       |

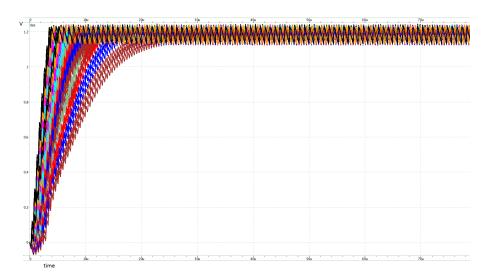

| 4.7  | Output voltage wave for various output currents                                             |

| 4.8  | Output voltage waveform for various input voltages                                          |

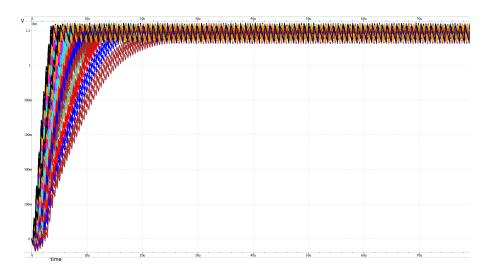

| 4.9  | Output voltage wave for various output currents at various corners                          |

| 4.10 | Output voltage wave for various output currents at various corners                          |

| 4.11 | Currents applied as loads                                                                   |

| 4.12 | Current applied as load                                                                     |

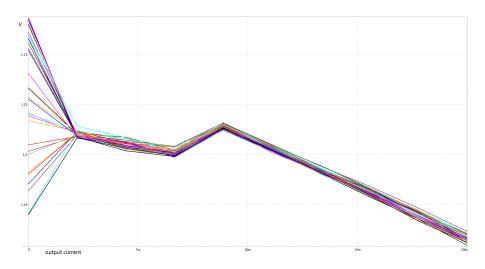

|      | Sweep of Io for an input of 0.8V                                                            |

| 4.14 | Sweep of $V_{DD}$ for a load of 20mA                                                        |

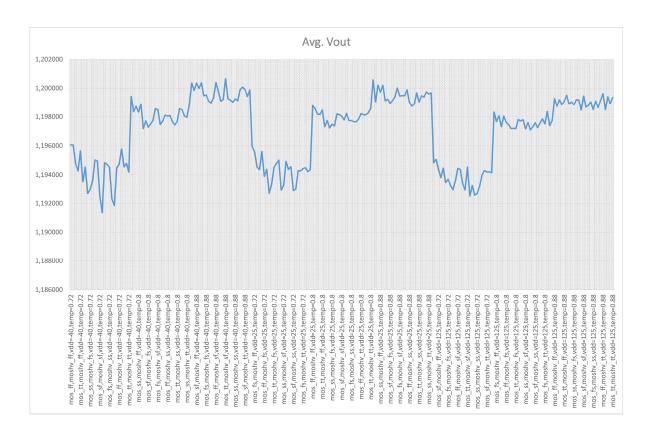

|      | Average output voltage of 100 instances of Monte Carlo for 24 PVT corners                   |

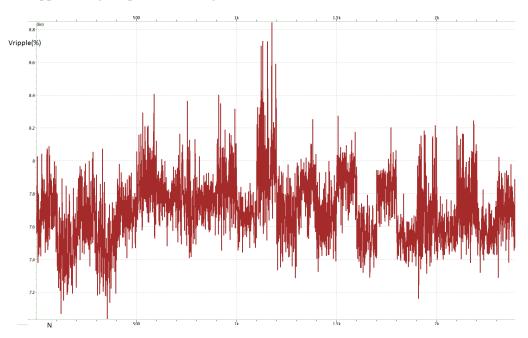

| 4.16 | Ripple voltage of 100 instances of Monte Carlo for 24 PVT corners                           |

| A.1  | This figure demonstrates the average $V_{out}$ in function of temperature and process       |

|      | for the proposed converter supplying an irregular load                                      |

| A.2  | This figure demonstrates the average $V_{out}$ in function of temperature and process       |

|      | for the proposed converter supplying an irregular load for each value of $V_{DD}$           |

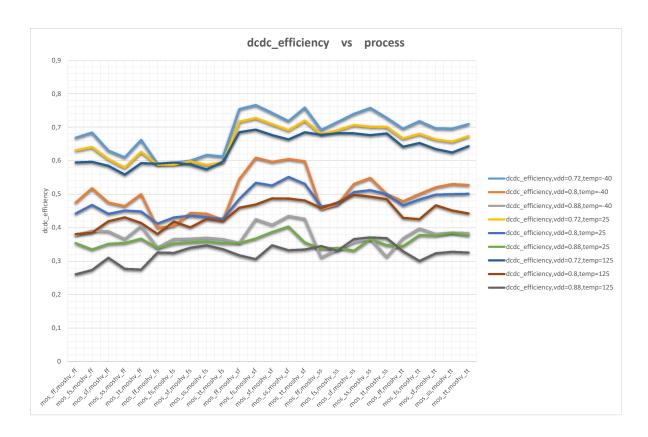

| A.3  | This figure demonstrate how Efficiency varies in function of the process for each           |

|      | temperature and $V_{DD}$                                                                    |

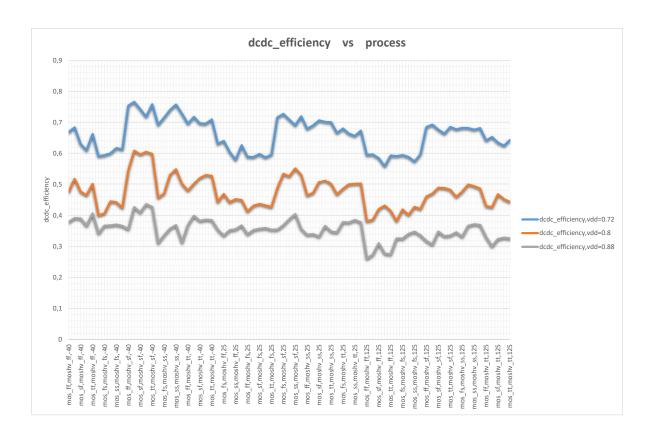

| A.4  | This figure demonstrate how Efficiency varies in function of the process and tem-           |

|      | perature for each value of $V_{DD}$                                                         |

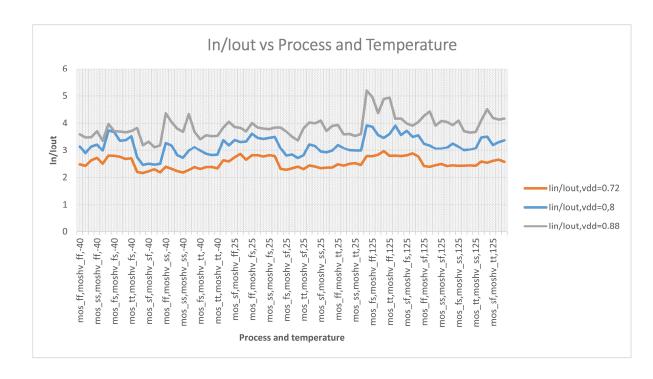

| A.5  | This figure demonstrates how $I_{in}/I_{out}$ varies in function of the process and temper- |

| 11.0 | ature for each $V_{DD}$                                                                     |

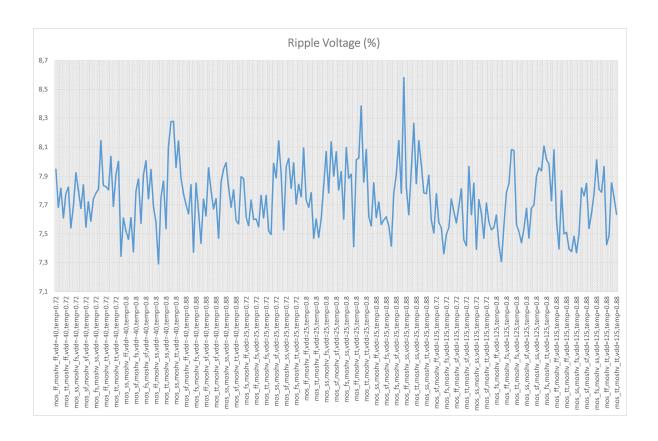

| A.6  | This figure demonstrates how the output ripple, in percentage, varies in function           |

| ,,   | of the process and temperature and $V_{DD}$                                                 |

|      |                                                                                             |

# **List of Tables**

| 3.1  | Performance goals                                           |

|------|-------------------------------------------------------------|

| 3.2  | Design parameters                                           |

| 3.3  | Requirement of a bi-level converter                         |

| 3.4  | Relevant Voltages in N-Stage Singular Bi-level Converter    |

| 3.5  | Relevant voltages of a two-stage dynamic CTS Charge Pump    |

| 3.6  | Comparative table of different bi-level converters          |

| 3.7  | Variation of Vgs Voltages for High Voltage transistors      |

| 3.8  | Parameters                                                  |

| 3.9  | Circuit Scenarios                                           |

| 3.10 | Summary table                                               |

| 4.1  | Metrics for circuit performance supplying a current of 10mA |

| 4.2  | Corner simulated for line regulation                        |

| 4.3  | Variable sweeped for line regulation simulation             |

| 4.4  | Test corner of irregular load simulation                    |

| 4.5  | Summary table                                               |

xiv LIST OF TABLES

## Abbreviations, Acronyms and Symbols

AC Alternate Current

CMOS Complementary Metal-Oxide-Semiconductor

CTS Charge Transfer Switch

DC Direct Current IC Integrated Circuit

NMOS N-type Metal-Oxide-Semiconductor OLED Organic Light-Emitting Diode PMOS P-type Metal-Oxide-Semiconductor

PWM Pulse Width Modulation PVT Process Voltage Temperature

Hz Hertz

nm nanometre

$V_{ov}$  Overdrive Voltage  $V_{th}$  Threshold Voltage

## **Chapter 1**

## Introduction

DC-DC converters have been the aim of much research and attention throughout time. Recently, with the increase in importance of portable devices, DC-DC converters became even more relevant. This is true because portable devices are battery supplied and batteries show varying voltage levels as they discharge, additionally subsystems of a device can have different energy requirements from what is made available by the main supply. Frequent solutions for DC-DC conversion involve inductors, however, for chip applications this is not desirable, since integrating inductors can be even impossible if above a few nano-Henrys and also they cause electromagnetic interference. First proposed by Cockcroft-Walton [1] Charge Pump circuits make DC-DC conversion possible using only capacitors switched in a controlled fashion through semiconductor devices. Later an integrated version was proposed by J. F. Dickson [2]. This work aims at researching existing topologies, evaluating them and designing a circuit architecture, in a 28nm process, with validation of performance parameters and robust to manufacturing imperfections, temperature and supply variation. Some contributions of this work include switches controlled with above supply levels, techniques to achieve such levels, and Pulse-Skipping plus Pulse Width control scheme to regulate the output to the target specifications. Also, challenges and solutions relating with full-corner validation are included, which is rarely occurring in most literature.

In short, the challenge is to design a Charge Pump based DC-DC converter fulfilling certain performance goals, mentioned later and with full-corner and monte-carlo validation. Techniques that focus on efficiency and area reduction are also used.

#### 1.1 Motivation

Power management is a fundamental issue in electronics. Devices can contain sub-systems that operate at specific voltages for which there isn't available supplies. This generalization includes a huge range of devices from industrial to domestic. Electronic devices that operate plugged-in into the grid may have transformers that change the voltage level of the AC supply to whatever is needed and then rectify the wave. But transformers are heavy and expensive and if different parts of the systems need different voltages it is much easier to use higher frequency switched DC-DC

2 Introduction

converters, because the higher frequencies allows for smaller and lighter transformers or inductors. With regard to on chip applications, this problem is even more important because inductors are hard to integrate and are limited to very low inductances. Furthermore, electronic devices such as laptops, cellphones and portable media players operate from batteries, which present a decaying voltage level as they discharge, along with having to supply sub-circuits with different voltage requirements. Charge Pumps offer the possibility to have DC-DC converters operating only with capacitors and semiconducting elements. Charge pump DC-DC converters have recently been applied in OLED displays [6], solar energy harvesting [7, 8] and even thermoelectric harvesting [9]. Also some others have been allowing the possibility of having multi-mode conversion capabilities in systems [10]. A few authors had objectives more similar to this work, such as avoiding inductors and using above supply gate signals in the operation of switches [11, 5]. The circuit that this work aims to achieve should be able to convert 0.8V to a stable 1.2V supply using a 28nm CMOS process. Moreover, it should be validated for all corner operation.

#### 1.2 Challenges and proposed solution

Challenges of this work involve choosing an adequate topology, keeping in mind the performance goals, which requires the understanding of the nuances of the different topologies and their trade-offs. As to be seen later, a big challenge to face is to adequately control the switches. These switches can be realized in different ways but turning them *on* and *off* in precise times is challenging. Their resistance, when conducting, is limited, requiring gate bootstraping techniques to achieve the goals. Gate bootstrapping is a technique that consists in using voltages higher than the supply at the gate of the transistor.

Ensuring that the circuit is robust to process, temperature and supply variations, is hard to accomplish since semiconductors' behaviour varies highly with these variables. Not all circuits will be able to handle such variations. A robust architecture that can deal with such variations will become a crucial factor in the design development.

Assuring an output as desired, a crucial factor for a DC-DC converter, when a load is unknown and can vary greatly requires some kind of close-loop control. A Pulse-Skipping with Pulse-Width-Modulation control will be used.

## 1.3 Objectives

The objective of this work is to design a converter fulfilling certain performance goals and validate the design for full corner operation. The goal is to convert a  $0.8V~(\pm 10\%)$  to a stable  $1.2V~(\pm 5\%)$  output able to supply a current up to 20mA.

#### 1.4 Dissertation Structure

The document is organized as follows:

1.4 Dissertation Structure 3

• Chapter 2 is intended to present the way Charge Pumps are typically made. The first Charge Pump known is presented, the Cockcroft-Walton Charge Pump. The Dickson Charge Pump in which a lot of Charge Pumps, to this day, are still based is mentioned. The CTS based Charge Pump that innovated the way Charge Pumps were made and is of particular importance to this work will be also presented. Finally, more recent topologies are presented. Throughout this chapter, there are references to articles and works devoted to the same aspects mentioned in the chapter. In short, this chapter exposes how Charge Pumps were developed throughout the literature, giving the reader tools to understand later different aspects of the present work.

- Chapter 3 explains the different steps taken during the design of the Charge Pump. It starts by giving the performance goals. Then it explains the operation of a Charge Pump and reflects on the topology choice. The requirement for the conception of the Bi-level converters, a crucial auxiliary circuit in the elaboration of the final circuit, is explained in this chapter. The way parameters are chosen and optimized as well as how the regulation of the output is achieved can also found here.

- Chapter 4 shows the final proposal and simulation results. Performance parameters will be simulated, such as, average output voltage, voltage ripple and efficiency. Many situations will be tested, including temperature extremes, process and mismatch deviations and variations of the input voltage.

- Chapter 5, the final chapter, presents some conclusions about this work and how this work can be improved further.

4 Introduction

## Chapter 2

# Background and Bibliographical Review

This chapter has two objectives: to present how Charge Pump based DC-DC converters were forged throughout time, explaining and commenting the advantages and problems of each version. The second objective is to give the reader tools to better understand the decisions taken in the design and also some working principles involved with it.

As a certain topology is discussed, bibliographical references will be presented, working principles will be explained and some aspects will be commented in what concerns their applicability.

#### 2.1 DC-DC converters

Electronic energy conversion consists in transforming electrical energy from one form to another, and the problem of how to make it efficiently and effectively as been posed to Engineers since electricity became a utility. The conversion may be concerned with voltage level adjustment, but may have to do with frequency conversion and also AC to DC or DC to AC are frequent needs. DC-DC converters are a subset of these in which only the voltage level is transformed. Throughout time this has been done in different ways. Before semiconductors, DC-DC conversion was achieved by first converting a DC supply to an AC voltage, changing the voltage level of the AC voltage with a transformer and only then to DC again. This, was possible because of the Vibrator [12], an electrical-mechanical device that allowed DC-AC and AC-DC conversion. The use of this primitive, but creative, DC-DC converter was mainly targeted for automobile radios and rural applications, where AC distribution was not present. Automobile radios needed high voltages to bias vacuum tubes used in radios and batteries were not able to offer such a high voltage. After the appearance of power semiconductors, this fell in disuse. DC-DC conversion is based on the principle of using energy storing elements, like inductors and capacitors, together with semiconductors, to produce a voltage level higher than the supply.

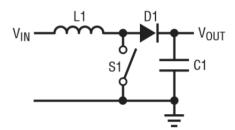

Figure 2.1 presents a basic DC-DC conversion topology using an inductor.

Figure 2.1: DC-DC converter using an inductor.

This is a typical DC-DC converter, an inductor is exposed to a source and energy is stored in its magnetic field. Later, when the switch opens, this energy is used to charge the capacitor through a diode. The rate of conversion (voltage level) can be controlled by the duty cycle of the switch. Although, not exactly like this, many circuits have been proposed that are inductor based [6, 7, 13, 14, 15], even though interesting, from a technological point of view, this type of converter will not be discussed beyond this, since it is inductor-based and out of the scope of this work.

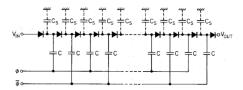

### 2.2 Cockcroft-Walton Charge Pump

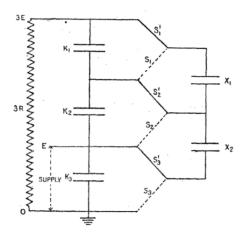

The first time a voltage multiplier was proposed that only used capacitors and semiconductors, seemed to be by Cockcroft and Walton in a work published in 1932 [1]. An interesting side-note is that Cockcroft and Walton were not trying to create a new capacitor based voltage multiplier, they were building a particle accelerator and a 800kV steady supply was needed. Its design can be seen in figure 2.2.

Figure 2.2: Cockcroft-Walton Charge pump, taken from [1].

The reason for building such a circuit, instead of other alternatives, like using a transformer to change the electrical distribution grid voltage into a higher voltage and then rectifying, is that they were trying to build this at reasonable cost and with ordinary laboratory equipment, as they said.

It consists of three capacitors in series and two other capacitors that are connected in a way that varies with the state of switches  $S_1$ ,  $S_2$  and  $S_3$ . There are two phases, Phase 1 corresponds to the full lines  $S_1'$ ,  $S_2'$ , and  $S_3'$  being connected and phase 2 corresponds to the dotted lines  $S_1$ ,  $S_2$  and  $S_3$  being connected. In the first phase the input supply charges  $K_3$  to potential E. Then, in the second phase,  $X_2$  is also charged by the supply. In the second phase 1,  $X_2$  shares its charge with  $K_2$ , and both will be charged to E/2 if their capacitance is equal. Following that, in the second phase 2,  $K_2$  will give half of its charge to  $X_1$  and both will have E/4. At the same time  $X_2$  is being charged to E, again. So, charge will gradually move through the capacitors until  $K_1$ ,  $K_2$  and  $K_3$  will have voltage E. At that point the output will be 3E. It also becomes obvious that adding more capacitors and switches will increase the multiplying factor and also that this principle is reversible meaning that if a supply of 3E is connect to what we currently consider the output,  $K_1$  will eventually have voltage E at its terminals. The way this is done no single capacitor withstands more that the voltage E at its terminals, and this is important because the voltage that capacitors are able to withstand is limited. It guaranties that no special higher voltage capacitor is needed. This was an important factor for them.

A doubling version of this, which is closer to what this works aims, can be seen in figure 2.3.

Figure 2.3: Double Cockcroft-Walton Charge Pump.

Capacitor  $K_2$  is in parallel with the source, as such it can be suppressed for boosting purposes, it serves only to highlight that if instead of where the load is connected a source was connected, capacitor  $K_2$  would finish with half the source's voltage (assuming both capacitors have the same capacitance). As Cockcroft and Walton, mentioned only two switches are necessary, besides  $S_3$  and  $S_3'$  in figure 2.2 the other switches can be replaced by diodes. The working principle can be extended to whatever integer multiplication value is needed. When supplying a load a ripple exists, the charge of  $K_1$  drops  $\delta \times V/R$ , being R the resistance of the load and  $\delta$  the duration of charge supplied by  $K_1$ . In the next phase,  $K_1$  must be able to recharge  $K_1$  and supply the load during that period; so, if both phases have the same duration  $K_1$  drains  $\delta \times VE/R$  from the load. Of course, this only works if the diodes allow the transfer of such charge in the existing time frame.

Although this a design is old, many of its principles can be extended to all charge pumps. In figure 2.4 it is possible to see how the circuit looks during phase 1, i.e.  $\Phi = 0$ , the top diode does not conduct. If one defines Q as the charge that the load absorbs during half period,  $X_1$  gains 2Q,

$K_1$  loses Q and  $K_2$  loses 3Q. Whatever charges are lost by the capacitors must be replenish during the next phase.

Figure 2.4: Phase 1 of the operation of the Cockcroft-Walton converter.

During phase 2 the circuit has the topology shown in figure 2.5. The load continues to absorb Q,  $X_1$  loses the 2Q that gained during the previous phase,  $K_1$  is recharged by Q, and  $K_2$  further discharges Q. This is the steady state operation of this circuit and naturally a ripple exists because  $K_1$ 's voltage is increasing in phase 2 and decreases during phase 1.  $K_2$  is put in parallel with a source, so it is being constantly replenished. The reason  $K_2$  is a capacitor and not just the source is suppose to be for two reasons: to highlight the fact the conversion works in both directions (if diodes are replaced by switches), and that at a certain point the source can be turned off without the converter stopping its operation. Of course the voltage will decreases through time but that may acceptable depending on the context.

Figure 2.5: Phase 2 of the operation of the Cockcroft-Walton converter.

In short, this topology opened a precedent for circuits that followed, at least some are loosely based on it. In comparison with other topologies more used in recent time, it has the advantage of limiting the voltage for each individual capacitor to the source's voltage. However, this topology becomes inefficient if implemented in a monolithic integrated form [3], this is because of the on-chip parasitic capacitance and also the output impedance increases rapidly with the number of multiplying stages.

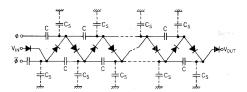

#### 2.3 Dickson Charge Pump

Another big step in Charge Pump history was made by John F. Dickson [2], he proposed an improved voltage multiplying configuration, for purposes of being integrated, known today as the Dickson Charge Pump and is shown in figure 2.6. The main difference between Dickson's Charge Pump and the Cockcroft-Walton are:

- In Dickson's Charge Pump individual capacitors have to withstand the full voltage developed along the chain. If maximum voltages for the process are respected this is not a problem.

- 2. The capacitors are coupled to the input via capacitors in parallel instead of in series. When in series, as Cockcroft-Walton, the effect of stray capacities is more dramatic.

Respectively, in figures 2.7 and 2.6 are represented the Cockcroft-Walton topology and Dickson's topology, each with their stray capacitances  $C_s$ .

Figure 2.6: Dickson Charge Pump with stray capacities, taken from [2].

Figure 2.7: Cockcroft-Walton Charge Pump with stray capacities, taken from [2].

Dickson argued that analysis of the Cockcroft-Walton circuit with stray capacitances is very complex but in practice, because of the stray capacitances, it is hard to obtain more than a doubler.

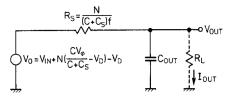

The configuration uses diodes, capacitors and two complementary squares waves to achieve its goals. The complementary signals are represented as  $\Phi$  and  $\bar{\Phi}$  in the figure. At the beginning of the operation when  $\Phi$  is low, the first capacitor C is charged to  $V_{in}-V_d$ , where  $V_d$  is the diode voltage drop. When  $\Phi$  becomes high the second capacitor is exposed to the voltage  $V_{in}-V_d+V_\Phi$  and it charges. Charge is pumped along the diode chain from the input to the output. Eventually the output reaches:

$$V_{out} = V_{in} + N(V_{\Phi} - V_d) - V_d \tag{2.1}$$

As pointed out in [4] if the stray capacitance  $C_s$  is considered, it reduce  $V_{\Phi}$  by a factor of  $C/(C+C_s)$  and also the presence of a load that draws  $I_{out}$  reduces the output voltage by  $N \cdot Iout/((C+C_s) \cdot f_{osc})$ , where  $f_{osc}$  is the operating frequency of the circuit, the output becomes:

$$V_{out} = V_{in} + N \cdot \left(\frac{C}{C + C_s} V_{\Phi} - V_d - \frac{I_{out}}{(C + C_s) f_{osc}}\right) - V_d$$

$$(2.2)$$

As Dickson pointed out:  $V_{out} = V_o - I_{out}.R_s$  where  $R_s = C/((C + C_s).f_{osc})$  and  $V_o = V_{in} - V_d + N \cdot C/(C + C_s) \cdot V_{\Phi} - V_d$

There is also a ripple associated with the operation of this circuit. When the last diode is not conducting, the the output capacitor is supplying the load and therefore it is discharging. In the next phase this capacitor is recharged. So the peak-to-peak ripple is:

$$V_{ripple} = \frac{I_{out}}{f \cdot C_{out}} \tag{2.3}$$

The equivalent circuit is represented in figure

Figure 2.8: Cockcroft-Walton Charge Pump with stray capacities, taken from [2].

The clock that Dickson used to apply to the capacitor was an oscillator with NMOS clock drivers, which does not allow for significant current delivery.

Dickson charge pump can be implemented in practice using diode-connected NMOS transistors, where the voltage drop  $V_d$  is the MOS threshold voltage  $V_{th}$ . This same voltage drop  $V_{th}$  makes it difficult for the Dickson topology perform charge operation at low voltages. Addressing this problem Wu [3] proposed a new version of the Dickson charge pump using static charge transfer switches (CTS), as discussed next.

## 2.4 CTS based Charge pumps

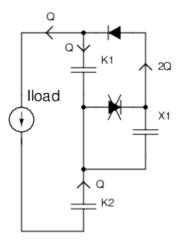

With Wu, Charge Pumps took yet another step forward, mainly concerned with low voltage operation, Wu proposed a way to eliminate voltage drops through diodes, that are present in Dickson's Charge Pump. Later in the text there will be a subsection devoted into looking at the topology proposed by Wu applied to this work, which holds testament to how significant this is for the study of Charge Pumps. The main idea behind the technique is to use MOS switches with precise on/off characteristics avoiding the forward voltage drop at each node. This can be observed in figure 2.9.

Figure 2.9: Static CTS based Charge Pump, taken from [3].

With the Dickson pump, the difference between the high level of two subsequent stages is:

$$G_{\nu} = V_{\Phi} \cdot \frac{C}{C + C_s} - Io \cdot \frac{C}{f \cdot (C + C_s)} - Vth. \tag{2.4}$$

This is called the pumping gain, and it reduces as  $V_{th}$  increases, as it does because of the body effect throughout the chain as  $V_{sb}$  voltage increases. So, this imposes a practical limit to the multiplication that can be achieved, due to the decreasing of the pumping gain.

Instead of the unavoidable voltage drop of the diode-connected MOS transistor, now the newly added transistors  $M_s$  1-5 have gate signals previously charged to make possible a fully charge of the output capacitor of a particular stage to the max voltage of the previous stage. Now the lowest voltage of stage n is the highest voltage of the n-1 and the voltage drop  $V_{th}$  disappears. The pumping gain defined as the difference between successive pump stages is  $G_v = V_2 - V_1 = \Delta V$  in which:

$$\Delta V = \frac{C}{C + C_s} \cdot V_{\Phi} - \frac{I_{out}}{(C + C_s) \cdot f_{osc}}.$$

(2.5)

However, this configuration has a problem, as pointed out by Wu himself, let us consider  $\Phi$  is low so nodes 2 and 3 are at  $2 \cdot \Delta V$  above node 1. This makes  $V_{gs}$  of  $M_{s2}$  be  $2 \cdot \Delta V$  which is above  $V_{th}$  (if it was not the charge pump would not work) so this transistor is not completely *off* and charge sharing in the reverse direction will occur. This was also addressed by Wu. By including pass transistors, NMOS and PMOS, it will be able to turn completely *off* the CTSs (charge transfer switches). This can be observed in figure 2.10.

Figure 2.10: Dynamic CTS based Charge Pump, taken from [3].

For this configuration to work two conditions have to be satisfied

$$2\Delta V > V_{tp} \tag{2.6}$$

and

$$2\Delta V > V_{tn} \tag{2.7}$$

As of the realization of the clock itself, Wu was more concerned in boosting its voltage than increasing its ability to deliver current. The converter he achieved had an output voltage of 2V and 10uA. A lot less (two thousand times) than what this works aims.

The mechanism used by Wu to get this clock is shown in 2.11.

Figure 2.11: Dynamic CTS based Charge Pump, taken from [3].

It allows the generation of a higher signal synchronous with the clock but its ability to deliver current is still limited to the  $R_{on}$  of transistors and the clock applied in these capacitors. This said, Wu's objective seemed to be to increase the practical limit of voltage multiplication and deliverable current was a secondary concern.

## 2.5 Modern Charge Pumps

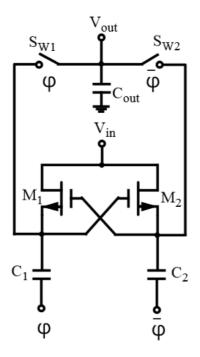

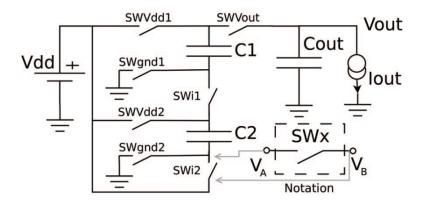

Recent history of Charge Pumps include a huge variety of designs, most are still strongly Dickson and Wu influenced [7, 8, 11, 5, 9]. As presented in [4], a Charge Pump that is used, at least partially, in other modern DC-DC converters, which is simple and power efficient is that proposed in [16] and of which the basic pumping cell is shown in figure 2.12.

When  $\Phi$  is low  $C_1$  is charged, and when  $\Phi$  is high  $C_2$  is charged. Eventually  $C_1$  and  $C_2$  will be charged to  $V_{in}$ , because Vgs of the transistors respectively charging each capacitor will be at  $V_{in} + V_{\Phi}$ , so nodes 1 and 2 (the top plate of each capacitor) will be alternately connected to  $C_{out}$ , in a way that  $C_{out}$  will only be connected to the node that is currently at  $V_{in} + V_{\Phi}$ . This is possible because of the  $S_{w1}$  and  $S_{w2}$  switches, which will also be controlled by  $\Phi$  and its complement.

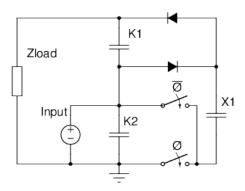

A design particularly interesting for this is work is presented in [5]. It consists in a series-parallel trippler. Two capacitors are charged in parallel with the voltage power source and then, in the subsequent phase, are in parallel with each other and the source to produce a higher voltage. Its topology is presented in figure 2.13.

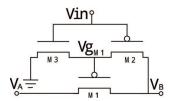

Figure 2.12: Modern Charge Pump, taken from [4].

The basic topology is simple, the challenge resides on the way switches are designed. Pérez-Nicoli proposes a special kind of switch seen in figure 2.14.

Figure 2.14: Switch proposed, taken from [5].

The transistor that actually transfers charge in the power part of the Charge Pump is M1. This is a PMOS, which is not as good as an NMOS would be, due to reduced mobility of holes when compared to that of electrons. This is a bi-phase converter. So during the phase when  $V_{in} = 0$ V, transistor M2 charges the gate of M1 to  $V_B$ , during this phase  $V_B$  is high so  $V_{gs}$  is 0V and the transistor is in cutoff. In the next phase  $V_{in} = V_{DD}$ , M3 discharges M1's gate and so M1 will be conducting and charging the capacitor. A very important point is that the charge used to charge and discharge the gate's capacitor is lost, as it will be referred later. This work will distinguish itself by using a mechanism in which charge is not lost. In Pérez-Nicoli's design the switch that connects to ground is just an NMOS transistor, since turning it on just requires a gate voltage higher than  $V_{th}$ .

Design of Charge Pumps is a diverse area of study, because some specific objectives such as energy harvesting focus more on having a high conversion ratio, many converter are micro-power

Figure 2.13: Series-Parallel Trippler, taken from [5].

and even nano-power and are not able of delivering significant currents. This work will focus more on output current than existing designs, so a series-parallel converter will be more appropriate. In this way the pulsating clock voltages that are applied in the base of capacitors are obtained from the source through bootstrapped switches, that are more capable to transfer current.

#### **2.5.1 Summary**

Under the light of the envisioned application, a Charge Pump circuit can vary a lot. Some are focused in higher conversion ratios and not on output current, some the opposite. Despite this, all topologies can be traced back the Cockcroft-Walton and Dickson Charge Pump. This is why they were presented here.

Cockcroft-Walton proposed a way of achieve a voltage level converter using only capacitors, also limiting the voltage in each individual capacitor. This opened the door for more work in capacitor based converters. Dickson concerns in achieving an on chip solution, originated into his own topology proposal that minimized the impact of stray capacitances. Wu improved upon this devising a dynamic way of turning *on* and *off* the switchs that are intended to transfer charge.

Many more Charge Pump were proposed with some nuances between them, however some of them have limitations on the clock's ability to deliver a charge to the load. This is a concern that will need to be addressed in this work.

## **Chapter 3**

## **Charge Pump Design**

This chapter is the core of this work, and accordingly it is mainly focused on the choice of the appropriate topology. An interesting approach commonly used to solve the problem is also analyzed here, together with a critical assessment on its benefits and limitations. It describes, step-by-step, the details of different parts of the system: main topology, switches, auxiliary circuits, regulation of outputs, etc. Also, details about circuit operation are presented, providing the necessary tools to understand the motivation behind the decisions made.

#### 3.1 Performance Goals

This work aims at designing a charge pump following a concrete set of goals, but keeping in mind important optimization parameters, such as area and energy efficiency. The set of specs to be met by the converter are presented in table 3.1. Other aspects such as, switch frequency, capacitor sizes and type of switches will be decided under the constrains of the goals.

Table 3.1: Performance goals

| Input Voltage   | 0.8V  |

|-----------------|-------|

| Input Tolerance | ±10%  |

| Output Voltage  | 1.2V  |

| Output Ripple   | ≤ 10% |

## 3.2 Operation with variation of PVT

A very important aspect that need to be considered during the design of a chip, and that distinguishes this work from most descriptions of Charge Pumps in literature, is a design oriented towards achieving performance goals are to be fulfilled even under PVT variations. PVT concerns the variation in process, voltage supply and operating temperature, which all influence chip operation. Wafers are fabricated in lots, and variation exists in electrical properties of the semi-conductors between lots and also slight variations within a lot. These process variations result

from deviations in the fabrication process, culminating in deviations of impurity concentration densities, diffusion depths and oxide thickness. This happens because environmental conditions may vary during crucial manufacturing steps, such as during depositions and diffusions of the impurities. All of this results in different transistor parameters, namely, different threshold voltages and different geometrical sizes of devices, mainly caused by the limited resolution of the photo-lithographic process. It leads to (W/L) variations in MOS transistors.

The effects these deviations have on device performance, either from environmental or process variations, are normally combined and translated in transistor models that reflect these variations in a slower or faster response. These are commonly referred as process corners and helps the designer to infer if its circuit is, or not, tolerant to fabrication variations along time. In principle, the actual devices are confined within the margins of the corners during production, and most of the times falling around the nominal values. Since CMOS technologies hold two types of transistors, NMOS and PMOS, five combinations define the limits, centred around the nominal: SS SF, TT, FS, FF, where S stands for "Slow", F for "Fast" and T for "Typical", which designates the nominal. The first letter always corresponds to NMOS and the second to PMOS. Actually, process corners is extended to other elements, such as resistors and capacitors, and all combinations normally need to be tested.

Supply voltage variation is taken into account in the performance goals by defining that the input voltage may vary within some margins, usually the slower corresponds to the minimum value and the fast the maximum, besides the typical. In the this work it is limited to -10% and +10% of the nominal voltage of 0.8V.

Chips often are exposed to very different temperatures. Beyond environmental conditions, temperature can be increased in a chip because of power dissipation during switching, short circuits occurring during transitions, caused by brief direct current from supply to ground, and also leakage currents. Electron and hole mobility in Silicon typically diminishes with temperature although the point at which the decrease begins depends on the doping. Also, the threshold voltage depends on temperature.

## 3.3 Charge Pump Topology

When choosing a topology it has to be taken into account the work already developed in charge pump topologies, mentioned in previous chapters. Most topologies are based on the conventional Dickson Charge Pump or the Series-Parallel converter. The Series-Parallel converter consists in charging a capacitor through a voltage power source and switches. Then that charged capacitor is put in series with the source, thereby producing a higher level voltage, as mentioned before. The Dickson Charge Pump consists in charging capacitors through a diode or switch. A clock voltage is applied to the bottom plate of the capacitors that when set to a high state raises the top plate voltage in relation to the reference. This higher level of voltage is now used to charge another capacitor, or to drive a load. A very important point to ask is where does the high level of the clock comes from?It may just come from a regular clock signal or from the input source

adequately switched. Note that the variation of charge at the top plate of the capacitor corresponds an equal amount of charge change (opposite sign) at the bottom plate. It is the clock that supplies that charge, meaning that the clock has to supply the same current that is delivered to the load or that charges a subsequent stage. The aforementioned current is as large as the load that is being supplied, thus, a simple logic clock cannot supply that kind of power. Somehow that power has to come from the input source, this important realization will be further explained in subsection 3.3.1.

Some topologies do not address the fact that there is a voltage drop across diodes or the switches. This has two obvious disadvantages:

- 1. Maximum achievable voltage is limited.

- 2. Resistance between stages. This limits the ability to share charge from successive stages. This limitation comes from the diode, and therefore it cannot be controlled beyond sizing it appropriately.

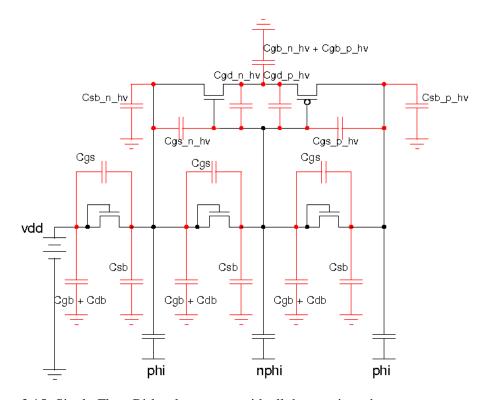

Where this is better addressed is in Wu's Dynamic Charge Transfer Switches citeWu1998. Many Charge Pumps appear to use this technique. The existence of the pass transistors allows the dynamical turning on and off of switches. Although interesting, this topology has its problems, which are explained in the subsection 3.3.2. Before explaining the limitations of the Dynamic CTS Charge Pump it is fundamental to understand the basic operation of the Charge Pump, explained in the next subsection.

#### 3.3.1 Basic operation of a Charge Pump

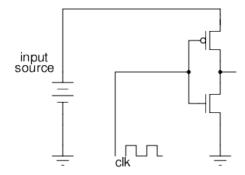

A crucial point made before is that, unless supplying very small currents, the clock signal used in many Dickson based Charge Pumps is a kind of a "Power Clock" in a way that the waveform is the same as the logical clock, but its ability to supply current has to be far greater. Because the only place that a large current can be drawn, in the circuit, is from the input power source, this "Power Clock" has to be the input source appropriately switched. This can be done with inverters, in a simple manner like that shown in 3.1.

Figure 3.1: Commutating the source with an inverter.

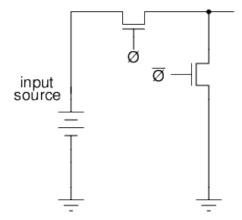

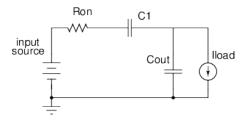

If large currents are to pass through this inverter, then low  $R_{on}$  resistance will be required. It may be done by increasing the W/L of the transistors but this will increase the gate capacitance that the clock has to charge and so significant current may be required from the clock itself in order to charge them. Of course this effect can be minimized by using a chain of inverters and with the clock charging only a minimal inverter. Still, as it will be explained further in this subsection, large average currents will have to be drawn from this device, this will require transistors with massive W/L to reduce their  $R_{on}$ . In addition to this, the number of inverters, their size, and frequency of operation will have a direct impact of the circuit consumption and it is desired to keep it as low as possible. This said, an alternative to use this inverter chain would be to use switches, just like the ones that may be use to charge the capacitor in the first place. A simple representation of this would can be seen in figure 3.2.

Figure 3.2: Opposite phase signal to switch the source.

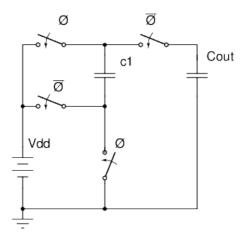

Of course, the signal controlling the switches cannot be the logical clock directly, a mechanism would be required to turn *off* and *on* the switches in an appropriate fashion. Wu addresses this by using pre-charged capacitors in addition to pass transistors to turn *off* and *on* the NMOS switches. Independently of the way switches are implemented, some conjectures can be made. Ignoring, momentarily how the switches are actually realized, a simplified representation of this circuit can be seen in figure 3.3.

The circuit operates in two phases. The Discharge phase consists in having  $C_{out}$  discharging to the load while  $C_1$  is charging trough a switch. An illustration of this can be seen if figure 3.4. The switch, that is in an *on* state is represented by its *on* resistance  $R_{on}$ . The charging of  $C_1$  follows the equation of a simple RC circuit, as expressed in equation 3.1.

$$V_{DD} \cdot u(t) = R_{on} \cdot i(t) + V_{C1}(t) \tag{3.1}$$

For our purposes,  $C_1$ , has an initial condition therefore it is important to include this fact in equation 3.1. Also, the voltage at  $C_1$  terminals is a result of accumulation of charge coming from

Figure 3.3: Switch based Charge Pump Topology.

the current flowing through it, so:

$$V_{DD} \cdot u(t) = R_{on} \cdot i(t) + V_{C1}(0) + \frac{1}{C1} \int i(t)$$

(3.2)

Applying the Laplace transform to equation 3.2.

$$\frac{V_{DD}}{s} = R_{on} \cdot i(s) + \frac{V_{C_1}(0)}{s} + \frac{i(s)}{C_1 \cdot s}$$

(3.3)

and then:

$$\frac{V_{DD} - V_{C_1(0)}}{s} = i(s)(R_{on} + \frac{1}{C_1 s})$$

(3.4)

$$i(s) = \frac{C_1(V_{DD} - V_{C_1}(0))}{RC_1 s + 1}$$

(3.5)

$$i(s) = \frac{\frac{V_{DD} - V_{C_1}(0)}{R_{on}}}{s + \frac{1}{RC_1}}$$

(3.6)

$$i(t) = \frac{V_{DD} - V_{C_1(0)}}{R_{on}} e^{\frac{-t}{R_{on} \cdot C_1}}$$

(3.7)

In equation 3.7 it is given the expression for the current in this part of the circuit and it can be seen that it starts from  $\frac{V_{DD}-V_{c1}(0)}{R_{on}}$  and approaches 0 as the capacitor reaches closer to the fully charged state.

As for the voltage:

$$V_{C_1}(t) = \frac{1}{C_1} \int i(t) \tag{3.8}$$

$$V_{C_1}(t) = (V_{DD} - V_{C_1}) \cdot e^{\frac{-t}{R_{On}C_1}} + C \cdot u(t)$$

(3.9)

Figure 3.4: Equivalent Circuit during discharge phase.

The constant that appears in result of the integration is resolved by satisfying the initial condition, and therefore we get:

$$V_{C_1}(t) = V_{DD} \cdot u(t) - (V_{DD} - V_{C_1}) \cdot e^{\frac{-t}{R_{on}C_1}}$$

(3.10)

From equation 3.7 we know that at t = 0 the voltage at the capacitor's terminals is  $V_{C_1}(0)$  and given enough time is  $V_{DD}$ .

During this phase the output capacitor is discharging.

$$V_{C_o}(t) = V_{C_o}(0) - I_o \cdot t \cdot u(t)$$

(3.11)

The current that  $C_{out}$  is supplying might not, and most probably is not, a direct current, however as long as the average current for this period does not exceed 20mA, the accepted ripple interval will be fulfilled, if the circuit is correctly designed.

At the beginning of this phase  $V_{out}$  should be at its maximum value of:  $1.2 + V_{ripple}/2$  and by the end it should not have gone below  $1.2 - V_{ripple}/2$ . This means that  $I_o \cdot T_{dis} \le C_{out} \cdot V_{ripple}$ , being  $T_{dis}$  the duration of the discharge phase.

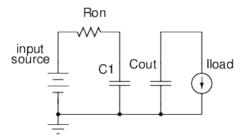

During the charge phase the circuit is a bit more complex, seen in figure 3.5. Now, the previous charged capacitor  $C_1$  is in series with the source and has to charge  $C_{out}$  as well as supplying the load during this period.

Figure 3.5: Equivalent Circuit during charge phase.

The equation for this period is the following, being  $C_{out}$  equal to  $C_o$ :

$$V_{DD} \cdot u(t) + V_{C_1}(0) \cdot u(t) - \frac{1}{C_1} \int i(t) = V_{C_0}(0) \cdot u(t) + \frac{1}{C_0} \int i(t) - Io \cdot u(t)$$

(3.12)

21

Applying the Laplace transform.

$$\frac{V_{DD} + V_{C_1}(0) - V_{C_o}(0)}{s} + \frac{Io}{C_o \cdot s^2} = i(s) \cdot \left(\frac{1}{s \cdot C_o} + \frac{1}{s \cdot C_1} + R_{on}\right)$$

(3.13)

$$\frac{s(V_{DD} + V_{C_1}(0) - V_{C_0}(0))}{R_{on}} + \frac{I_o}{R_{on}C_o}$$

$$s \cdot \left(s + \frac{1}{R_{on}C_o}\right)$$

(3.14)

$$i(s) = \frac{\frac{s(V_{DD} + V_{C_1}(0) - V_{C_0}(0))}{R_{on}} + \frac{I_o}{R_{on}C_o}}{s \cdot \left(s + \frac{1}{R_{on}C_o}\right)}$$

(3.15)

$$i(s) = \frac{\frac{s(V_{DD} + V_{C_1}(0) - V_{C_0}(0))}{R_{on}} + \frac{I_o}{R_{on}C_o}}{s \cdot \left(s + \frac{1}{R_{on}C_o}\right)} = \frac{A}{s} + \frac{B}{s + \frac{1}{R_{on}C_{eq}}}$$

(3.16)

In which:

$$C_{eq} = \frac{C_o C_1}{C_o + C_1} \tag{3.17}$$

and then:

$$A = \frac{I_o C_1}{C_o + C_1}, B = \frac{(V_{DD} + V_{C_1}(0) - V_{C_o}(0))}{R} - \frac{I_o C_1}{C_o + C_1}$$

(3.18)

Returning to the time domain:

$$i(t) = \frac{I_o C_1}{C_o + C_1} u(t) + \left( \frac{(V_{DD} + V_{C_1}(0) - V_{C_o}(0))}{R_{on}} - \frac{I_o C_1}{C_o + C_1} \right) \cdot e^{\frac{-t}{R_{on} C_{eq}}}$$

(3.19)

As in the previous phase, the voltage at its terminals is just the primitive of the current divided by the capacitance.

$$V_{C_o}(t) = -\frac{1}{C_o} \int i(t)$$

(3.20)

Resolving the primitive:

$$\frac{-I_o}{C_o + C_1} t u(t) + \left[ R_{on} I_o \left( \frac{C_1}{C_o + C_1} \right)^2 - \left( V_{DD} + V_{C_1}(0) - V_{C_o}(0) \right) \frac{C_1}{C_1 + C_o} \right] e^{\frac{-t}{R_{on} C_{eq}}} + C \cdot u(t) \quad (3.21)$$

Resolving the constant C:

$$Vo(t) = \frac{-I_o}{C_o + C_1} \cdot t \cdot u(t) + \left[ R_{on} I_o \left( \frac{C_1}{C_o + C_1} \right)^2 - (V_{DD} + V_{C_1}(0) - V_{C_o}(0)) \frac{C_1}{C_1 + C_o} \right] e^{\frac{-t}{R_{on} C_{eq}}} + \left[ (V_{DD} + V_{C_1}(0)) \frac{C_1}{C_1 + C_o} + V_{C_o} \frac{C_o}{C_o + C_1} - R_{on} I_o \left( \frac{C_1}{C_o + C_1} \right)^2 \right] u(t) \quad (3.22)$$

Because of the action from the current source that is drawing current, given enough time the capacitors will eventually discharge completely, but for correct dimensions, the voltage first increases before starting to fall, defining a point of maximum voltage.

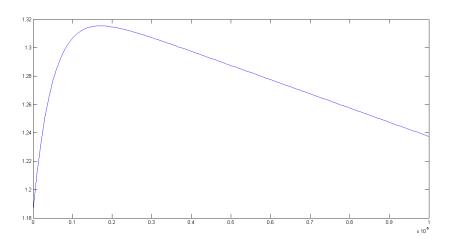

For the values expressed on table 3.2, chosen arbitrarily just to indicate how the voltage would vary in time during the discharge phase, results in waveform presented on figure 3.6

Table 3.2: Design parameters.

| Parameter   | Value     |

|-------------|-----------|

| $V_{dd}$    | 0.8V      |

| Io          | 20mA      |

| $R_{on}$    | $1\Omega$ |

| $V_{c1}(0)$ | 0.7V      |

| $V_{co}(0)$ | 1.185V    |

| $C_1$       | 100nF     |

| $C_o$       | 100nF     |

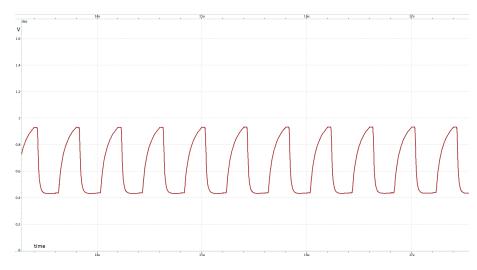

Figure 3.6: Voltage waveform during discharge phase.

Ideally, for the worst possible corner, the discharge phase would be set to end by the clock control, when the maximum voltage is reached. As such, it is desirable to locate the maximum value of the voltage as function of time. That can be resolved by finding the point the derivative

23

passes through 0.

$$\frac{d}{dt}V_o(t) = 0 (3.23)$$

$$\frac{d}{dt}V_{o}(t) = -\frac{I_{o}}{C_{o} + C_{1}}u(t) + \left[ -\left(\frac{C_{o} + C_{1}}{RC_{o}C_{1}}\right) \left(\frac{I_{o} \cdot R_{on} \cdot C_{1}^{2}}{\left(C_{o} + C_{1}\right)^{2}} - \left(V_{DD} + V_{C_{1}}(0) - V_{C_{o}}(0)\right)\right) \frac{C_{1}}{C_{1}C_{o}} \right] e^{\frac{-t}{R_{on}C_{eq}}}$$

(3.24)

with further manipulation:

$$t_{opt} = -\ln\left(\frac{C_o}{\frac{(V_{DD} + V_{C_1}(0) - V_{C_o}(0))(C_o + C_1)}{RI_o} - C_1}\right) \frac{RC_oC_1}{C_o + C_1}$$

(3.25)

Substituting  $C_{out}$  by C and  $C_1$  by  $\alpha \cdot C$ , in which  $\alpha$  is the relation between the capacitors, results in:

$$t_{opt} = -\ln\left(\frac{1}{\frac{(V_{DD} + V_{C1}(0) - V_{Co}(0))(1+\alpha)}{R_{on}I_o}} - \alpha\right) \frac{\alpha}{1+\alpha} R_{on}C$$

(3.26)

It is vital to know if  $t_{opt}$  is not positive which would mean that the voltage does not rise and therefore the output capacitor instead of charging is further discharged. For  $t_{opt}$  to be positive:

$$\frac{C_o}{\frac{(V_{DD} + V_{C_1}(0) - V_{C_o}(0))(C_o + C_1)}{R_{on}I_o} - C_1} < 1$$

(3.27)

so the condition that needs to be satisfied is:

$$R_{on} < \frac{V_{DD} + V_{C1}(0) - V_{Co}(0)}{Io}$$

(3.28)

To have a better notion of the values involved, in the worst corner case  $V_{DD}$  is 0.72V.  $V_{C1}(0)$ , which is the voltage at capacitor  $C_1$  at the beginning of this phase (this voltage is generated by charging this capacitor in the previous phase), in the best possible case is very close to 0.72V. For the purpose of this argument lets assume it is 0.72V. Now considering that  $V_{Co}(0)$  is 1.2V -  $\frac{V_{ripple}}{2}$  which is 1.17V, this leads to:

$$R_{on} < 13.5\Omega \tag{3.29}$$

The condition in equation 3.29 is necessary for the capacitor  $C_o$  to charge. However that does not mean that the maximum value will actually be reached. There are other factors to take into consideration, like capacitance, frequency of operation, etc... Thus, another pertinent expression to be found is the value for the maximum voltage. This occurs at  $t = t_{opt}$ . So, substituting 3.26 in 3.22 results in:

$$V_{max} = \frac{R \cdot I_{o} \cdot \alpha}{(1+\alpha)^{2}} \cdot \ln \left( \frac{1}{\frac{V_{DD} + V_{C1}(0) + V_{Co}(0)}{R_{on} \cdot I_{o}}} (1+\alpha) - \alpha \right) + \left[ R_{on} \dot{I}_{o} \frac{\alpha}{1+\alpha} - \frac{V_{DD} + V_{C1}(0) + V_{Co}(0) \cdot \alpha}{1+\alpha} \right] \frac{1}{\frac{V_{DD} + V_{c1}(0) - V_{co}(0)}{R_{on} \cdot I_{o}}} + \frac{1}{R_{on} \cdot I_{o}} (V_{DD} + V_{c1}(0)) \frac{\alpha}{1+\alpha} + V_{co}(0) \frac{1}{1+\alpha} - R_{on} \cdot I_{o} \frac{\alpha}{(1+\alpha)^{2}}$$

(3.30)

A very important realization that comes from 3.30 is the fact that the maximum value of the voltage does not depend on the absolute size of capacitors but rather on the ratio between them.

It is important to notice that for  $C_1$  to charge  $C_{out}$  and supply the load, assuming the load current for an entire period has an average value of  $I_o$ , the total charge transferred by  $C_1$  has to be  $I_o.T$ . This is because  $C_1$  is discharged by  $I_o.T_{dis}$  in the previous phase, and during this phase the load further absorbs  $I_oT_{char}$ , being  $T_{char}$  the duration of this phase.

Looking now into how these switches are actually realized, the simplest way is to use a single transistor with appropriate gate levels. When choosing between an NMOS or PMOS transistor, the obvious choice is NMOS because the mobility of holes is less than that of electrons and low resistance will be vital in the process. The applied gate signal has to fulfil some requirements:

- During those phases that the switch should be off, applying a low enough gate voltage to have a  $V_{gs} < V_{th}$ .

- When the switch should be on, apply a high enough voltage to eliminate the voltage drop  $V_{th}$ , so  $V_{gb} > V_{db} + V_{th}$ . This condition allows to charge the capacitor to the voltage of the previous stage. If  $V_{gb}$  is lower than this, the transistor enters the cut-off region before the capacitor reaches its maximum achievable voltage.

- The higher  $V_{gb}$  gets, the higher  $V_{gs}$  gets. This leads to a low  $R_{on}$  which is very desirable, although  $V_{gs}$  should not surpass the max voltage that the transistor withstands to avoid damaging it or accelerate its ageing process.

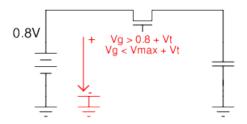

A representation of this can be seen in figures 3.7 and 3.8. There we can observe the intervals that Vg voltage has to fulfil.

The way these gates are charged and how to respect these intervals will be addressed in section 3.4.

Turning *off* and *on* NMOS switches dynamically is better addressed in Wu's dynamic charge transfer switches charge pump citeWu1998. Although interesting, this topology has its own limitations. This will be tackled in the next section.

Figure 3.7: Turning on a NMOS switch.

#### 3.3.2 Dynamic CTS Charge Pump: Advantages and limitations

The main advantage of the Dynamic CTS Charge Pump is that it uses pre-charged capacitors to turn *on*, turn *off*, and bootstrap gates. This means, that this circuit can be realized with a certain area-saving factor.

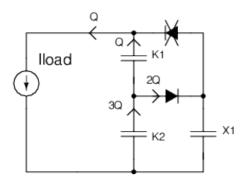

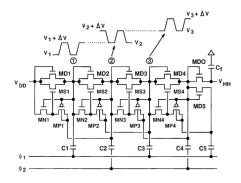

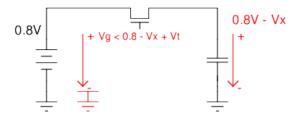

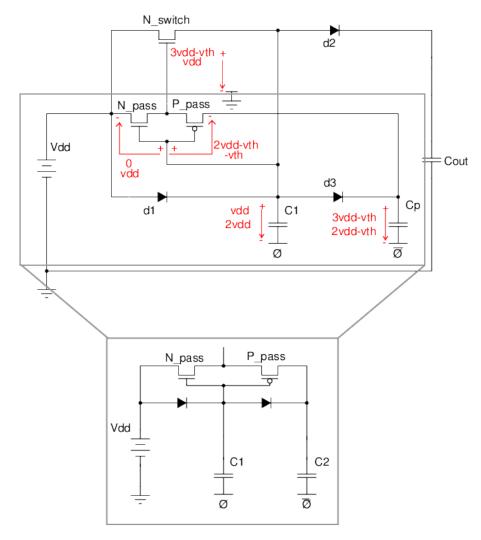

In figure 3.9, we present a two stage dynamic CTS charge pump circuit. Also, for each relevant voltage there are two values, one corresponding to each phase in some circuit elements.

A simple description of the operation of this circuit follows:

- Phase  $\phi = 1$  1. N\_pass is turned off because of a  $V_{gs}$  of '0V'.

- 2. P\_pass is turned on because of a  $V_{gs}$  of  $2V_{DD} V_{th}$ , assuming that  $2V_{DD} V_{th} > V_{th}$ .

- 3. Because of the two previous facts the  $V_{gb}$  of N\_switch is charged to the voltage of the top plate of Cp,  $3V_{DD} Vth$ .

- 4.  $3V_{DD} V_{th} > V_{DD} + V_{th}$ , so the capacitor  $C_1$  is charged to  $V_{DD}$ .

- During this phase, C<sub>out</sub> might be supplying charge to loads, and therefore is discharging.

- Phase  $\phi = 0$  1. The voltage at the top plate of  $C_1$  rises to  $2V_{dd}$ .

- 2.  $C_1$  charges  $C_p$  through diode d3.

- 3. N\_pass is turned on.

- 4. P\_pass is turned off.

- 5. The gate of N\_switch discharges to  $V_{DD}$ .

- 6. The source and gate of N\_switch are at the same voltage, so N\_switch is turned *off*. This avoids transference of charge in the reverse direction.

- 7. The top plate of  $C_1$  is now at  $2V_{DD}$  so it charges  $C_{out}$  through diode d2.

The last voltage drop from  $C_1$  to  $C_{out}$  is not avoided. A very important point is that the ability do deliver charge to a load is limited by the ability to transfer charge throughout pumping stages. This means that for  $C_{out}$  to deliver a certain amount of charge during a certain phase, in the next phase  $C_1$  has to, not only recharge  $C_{out}$ , but also needs to have enough charge left to supply the load during this phase, this has all to be done without its voltage dropping beyond a certain point.

As seen in figure 3.9, the largest  $V_{gs}$  of the N\_switch is  $2V_{DD} - V_{th}$ . This might be enough to charge the subsequent capacitor to  $V_{DD}$ , but equally important is if it reduces  $R_{on}$  enough.

Figure 3.8: Turning off a NMOS switch.

Additionally, a trade-off is involved between having a  $V_{gs}$  big enough to reduce  $R_{on}$ , but small enough not to damage the transistor.

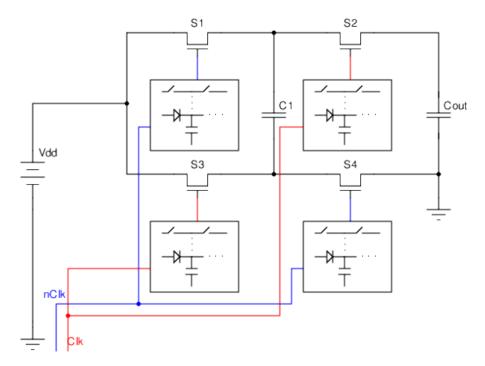

#### 3.3.3 Choice of Topology

Since an important criteria is to deliver a significant amount of current, the topology proposed by this work is based on figure 3.3. Switches will be NMOS transistor with bi-level converters to charge the transistor's gate. Bi-level converters will be presented in the next section. In figure 3.10 a diagram is shown with the proposed solution.

The question that emerges is how to design these blocks that have to control the gate voltage of the NMOS. These will be Charge Pump based circuit, that will be further explored in the next section.

#### 3.4 Bi-level Converter

From what has been seen before there is a necessity to obtain certain levels of voltage to turn *off* and *on* the NMOS switches in an appropriate way. The way this is done is a crucial part of this work. This chapter will be devoted to analyse the operation of these type of converters, some simulations are made mainly to highlight circuit limitations. Some details might not be mentioned if they are not relevant. Conclusions shown here will be helpful to understand how to design the necessary bi-level converters, however this chapter is not about obtaining the dimensions of a specific design, its about general conclusions and details about these converters and their specificities, which are not described in most DC-DC converter reports found in literature.

First, it is important to understand what is needed from a bi-level converter. The output of this circuit will oscillate between two values:  $V_{low}$  and  $V_{high}$ .  $V_{low}$  must turn off the NMOS,  $V_{high}$  must turn it on, but must be low enough not to damage the transistor.

In table 3.3 the required voltages for a certain bi-level converter are presented.

Table 3.3: Requirement of a bi-level converter.

$$egin{array}{c|c} V_{low} & < V_{sb} + Vt \\ V_{high} & > \tilde{V_{sb}} + Vt \text{ and } < V_{max} \\ \end{array}$$

To turn the transistor off, it must set to be in cut-off region assured by having  $V_{gs} < V_{th}$ , turning on requires  $V_{gs} > V_{th}$ , but as the next capacitor charges the transistor, it enters in cut-off region so

3.4 Bi-level Converter 27

Figure 3.9: Two-stage Dynamic CTS Charge Pump.

the voltage must be  $V_{th}$  above whatever voltage we desire to transfer. The voltage that is wished to transfer is denominated  $\tilde{V_{sb}}$ . Also,  $V_{gs}$  must be limited to the maximum voltage that the transistor is able to withstand.

All of this has to be taken into account when designing a bi-level converter because the consequence of having one switch not being turned *off* or *on* adequately is dire to the circuit. The next section will go into details about the way a bi-level converter works, vital information to understand how to design this converter is also presented. Every bi-level will be sensible to PVT corners so some sort of controller will be needed to regulate it. This will be tackled later in this work.

#### 3.4.1 General Operation

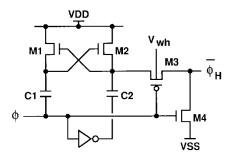

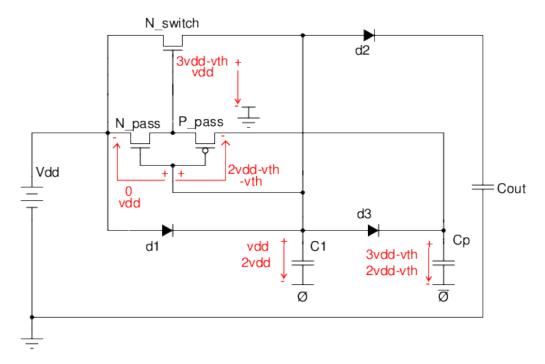

A mechanism was devised to accomplish the goal of generating two voltage levels using charge pump converters denominated as "bi-level converters". From a certain input, it generates two different values of voltage that are alternated. Turning *on* and *off* an NMOS switch is done by applying the appropriate gate signals, as seen. Figure 3.11 highlights the mechanism by which this is done in the Dynamic CTS converter.

Two parts of this circuit can be distinguished, one being the power part, that is the part in which charge circulates with the purpose of actually supplying the load, the other is the bootstrapping part that exists to control the gates of the NMOS switches. An important factor is that in Wu's Dynamic CTS these two parts overlap in capacitor  $C_1$ . This has two advantages:

Figure 3.10: Proto-bi-level.

- A capacitor is saved from the bi-level charge pump part, although this capacitor would be significantly smaller as the ones from the power part.

- This capacitor alternates between  $V_{DD}$  and  $2V_{DD}$  instead of  $V_{DD} V_t$  and  $2V_{DD} V_t$ .

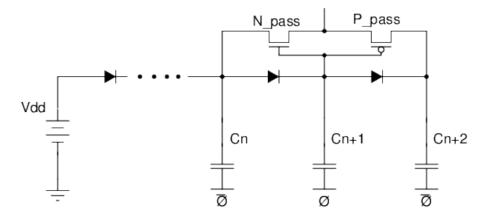

However the peak-to-peak voltage of the wave generated by the converter seen in figure 3.11, might not be enough for turning *off* the switch in one period and turning *on* in the other. A solution would be to add a previous stage as seen in figure 3.12.

The addition of pre-stages allows for higher voltages to be attained, the mechanism of achieving the alternate wave is the same but the inclusion of more stages increases the alternating levels. The voltage variation mechanism can be seen in table 3.4.

Table 3.4: Relevant Voltages in N-Stage Singular Bi-level Converter.

| Phase      | $C_n$              | $C_{n+1}$                 | $C_{n+2}$               | Vgs(N_pass)    | Vgs(P_pass)     | Drain                   |

|------------|--------------------|---------------------------|-------------------------|----------------|-----------------|-------------------------|

| Φ          | $nV_{DD}$ - $nVt$  | $(n+2)V_{DD}$ - $(n+1)Vt$ | $(n+2)V_{DD} - (n+2)Vt$ | $2V_{DD} - Vt$ | Vt              | nV <sub>DD</sub> - nVt  |

| $ar{\Phi}$ | $(n+1)V_{DD}$ -nVt | $(n+1)V_{DD}$ - $(n+1)Vt$ | $(n+3)V_{DD} - (n+2)Vt$ | -Vt            | $-2V_{DD} + Vt$ | $(n+3)V_{DD} - (n+2)Vt$ |

One important note is the values under  $C_n$  are not the actual voltage between the capacitor's terminals as this voltage does not vary much in steady state, it is the voltage at the top plate of the respective capacitor.

The aspect of the waves in each stage can be seen in figure 3.13. This is a result of a simulation of a partial converter with no pass transistors, just the diodes and capacitors, to better understand what happens when they are added.

3.4 Bi-level Converter 29

Figure 3.11: Proto-bi-level converter of Dynamic CTS charge pump.

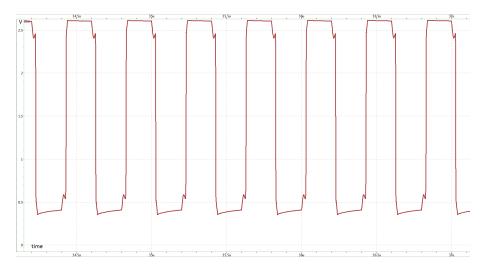

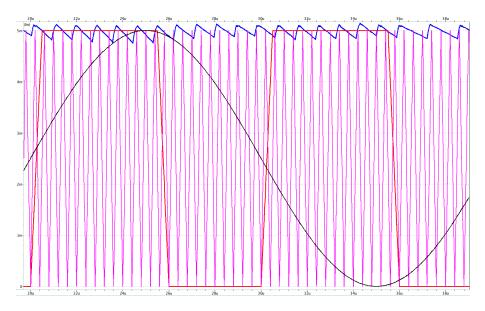

Figure 3.13: Wave aspect for each stage in Bi-level converter (First stage in brown, second stage in blue and third stage in red).

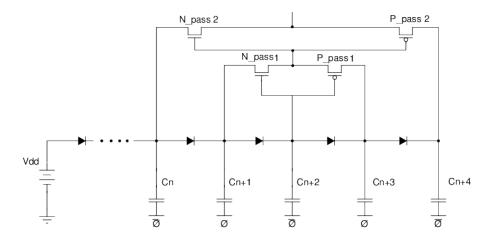

Figure 3.12: N-stages Singular Bi-level Converter.

The analyses of this is quite straight forward. Each stage alternates between a high and low voltage level. When a certain stage is high it charges the next stage voltage, which is  $V_{th}$  smaller than that of the previous stage. That stage then switches to the high voltage and charges the next stage. Adding the pass transistors makes it possible for an output capacitor to be charged to the highest voltage of the last stage, and discharged to the lowest voltage of the first stage in the next phase.

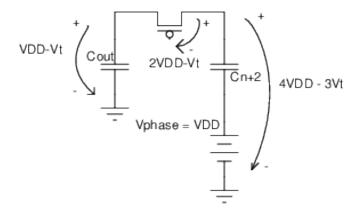

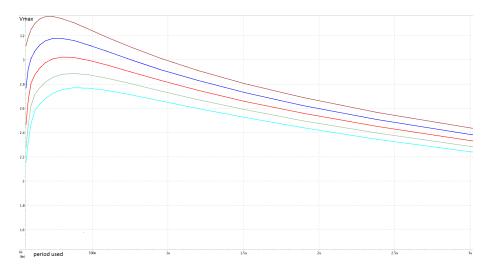

Looking in more detail into the pull-up part, as in figure 3.14. It may take some time for the capacitors to finish their charge transfer, but it is desirable that the final voltage of both capacitor is much closer to  $4V_{DD} - 3V_t$ , this final value is given by 3.31.

Figure 3.14: Aspect of circuit part responsible for charging the output.

$$V_{finalpullup} = \frac{C(4V_{DD} - 3Vt) + C_{out}(V_{DD} - Vt)}{C + C_{out}}$$

(3.31)

In the pull-down the analogous happens:

$$V_{final pull down} = \frac{C(V_{DD} - Vt) + C_{out}(4V_{DD} - 3Vt)}{C + C_{out}}$$

$$(3.32)$$

3.4 Bi-level Converter 31

From this it possible to get the difference between the high level and the low level, an important information when designing a bi-level converter for a switch, having:

$$V_{pp} = \frac{C(4V_{DD} - 3Vt) + C_{out}(V_{DD} - Vt) - C(V_{DD} - Vt)}{C + C_{out}}$$

(3.33)

Simplifying the equation:

$$V_{pp} = \frac{C(3V_{DD} - 2Vt) - C_{out}(3V_{DD} - 2Vt)}{C + C_{out}}$$

(3.34)

If the  $C_{out}$  is defined as a proportion of C,  $C_{out} = \alpha$  C.

$$V_{pp} = C(3V_{DD} - 2Vt).\frac{1 - \alpha}{1 + \alpha}$$

(3.35)

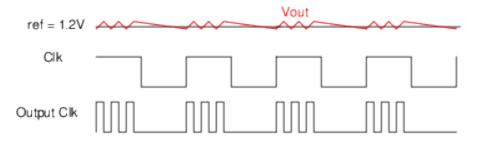

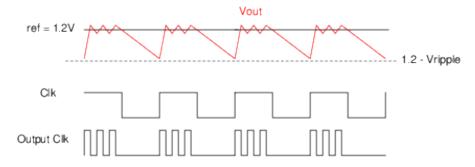

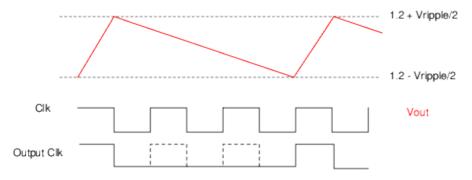

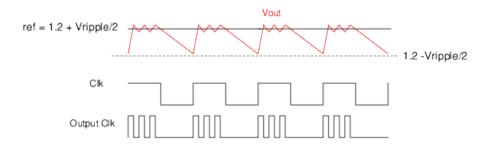

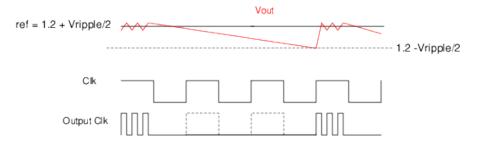

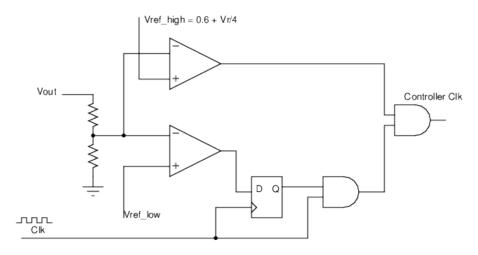

$C_{out}$  is whatever load capacitance the pass transistors are charging but it always includes the stray capacitances between the drain and substrate of the two transistors, so increasing W to reduce their pull-up and pull-down resistance also increases their stray capacity that reduces  $V_{pp}$ . Of course, if  $C_{out}$  is much bigger than the strays, then there will be no impact.