#### FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# **Energy and Temperature Aware Real-Time Systems**

Muhammad Ali Awan

**DISSERTATION**

Doctoral Program in Electrical and Computer Engineering

Supervisor: Stefan Markus Ernst Petters

September 16, 2014

### **Energy and Temperature Aware Real-Time Systems**

#### Muhammad Ali Awan

Doctoral Program in Electrical and Computer Engineering

### Approved by:

President: Dr. Jose Alfredo Ribeiro da Silva Matos

External Referee: Dr. Gerhard Fohler External Referee: Dr. Marko Bertogna

FEUP Referee: Dr. Luis Miguel Pinho Almeida FEUP Referee: Dr. Mario Jorge Rodrigues de Sousa

Supervisor: Dr. Stefan Markus Ernst Petters

### **Abstract**

Modern embedded systems have increasingly penetrated our daily life, and have facilitated and accelerated our regular activities. Some of these systems are constrained with strict timing requirements, and have limited and/or intermittent power supply. One of the major challenges in the design process of such systems is to minimise their energy consumption and thus to increase the battery life and enhance their mobility. In order to address this objective, it is important to understand the current trends in the embedded systems industry. With progressing CMOS technology miniaturisation, the leakage power dissipation — once neglected — has become a major contributor to the overall power dissipation of modern embedded systems and as a matter of fact it has started to dominate its counterpart, the dynamic power dissipation. To cope with current trend of increasing leakage current, hardware vendors have equipped modern embedded processors with several sleep states and reduced the overhead (energy/time) of a sleep transition. Secondly, there is a trend towards an increased number of devices, as an ever increasing need for extra functionality in a single embedded system demands for extra Input/Output (I/O) devices, which are expensive in terms of energy consumption. Similar to processors, these devices are also equipped with low power sleep states to reduce their energy consumption. Thirdly, modern embedded processors have started to suffer from thermal issues due to increase in power density. It is essential to keep the temperature within recommended limits for the safe operation of the system and to increase the durability/reliability of hardware platforms. Finally, the CMOS industry experienced a paradigm shift in the last decade from single processor design to multicore hardware platforms as the clock frequency cannot be further increased efficiently to enhance the performance of the system. This is driven by the increase in performance per watt ratio that demands special packaging techniques to dissipate the generated heat at high frequencies.

This dissertation attempts to provide energy efficient solutions and techniques to cope with the aforementioned arising trends, while closing the gap between theoretical research and practice. In particular, it focuses at the operating-system-level power management and exploits the available sleep states to improve on energy efficiency while mainly concentrating on the leakage power dissipation. Uniprocessor power management has been widely explored in the last two decades. Several procrastination approaches has been proposed in the literature to deal with the leakage current. However, these solutions approximate the procrastination interval to ease the analysis and sub-optimally utilise the available resources to minimise energy consumption. Such approximation is eliminated in this dissertation with the optimal algorithm to maximise energy savings. A practical limitation of the procrastination scheduling algorithm is relaxed by eliminating the need for an external hardware to implement the power saving algorithm. These newly developed algorithms with low complexity save energy comparable to procrastination scheduling. Furthermore, this dissertation demonstrates that idealised dynamic voltage and frequency scaling, and the thermally constrained dynamic power management are equivalent in nature. Hence, existing solutions proposed for dynamic voltage and frequency scaling can be easily ported to increase energy efficiency in thermally constrained systems.

Intra-task I/O device scheduling was vastly ignored in the past due to an increased overhead of sleep transitions. A decrease in sleep transition overheads allows to explore this new paradigm of device scheduling. This solution not only minimises the pessimism involved in traditional device scheduling algorithms but also reduces the online overhead of scheduling algorithms and has the flexibility to scale easily with an increase in I/O devices. Finally, this dissertation addresses the power management in the context of multicore hardware platforms. Global scheduling algorithms have become an attractive choice to schedule applications on a homogeneous multicore platform. The proposed energy saving algorithm exploits the spare capacity in the schedule and exploits the sleep states available in homogeneous multicore platform to save energy consumption. Heterogeneous multicore platforms are famous in modern computing to perform specific tasks efficiently. Energy efficient mapping on heterogeneous multicore platforms addressed in the literature considers only dynamic power dissipation while assuming leakage power dissipation a constant factor. Opposed to the state-of-the-art, the proposed allocation heuristics in the thesis are divided into two phases to tackle both dynamic and leakage power dissipation. All the algorithms proposed in this dissertation are evaluated with extensive set of simulations for a variety of hardware platforms and workloads.

### Resumo

É um facto constatado que os sistemas embebidos têm tomado um lugar relevante na nossa vida quotidiana, tendo facilitado e até acelerado as nossas actividades diárias. Alguns destes sistemas caracterizam-se por requisitos temporais bastante rigorosos e são alimentados por fontes de energia limitadas e/ou intermitentes. Um dos maiores desafios no projecto deste tipo de sistemas consiste em minimizar o seu consumo de energia e, consequentemente, aumentar a sua autonomia e mobilidade. De forma a atingir este objectivo, é fundamental compreender as tendências actuais na indústria dos sistemas embebidos. Com a progressiva miniaturização da tecnologia CMOS, a potência devida à corrente de fuga - anteriormente desprezável - tornou-se numa das principais contribuições para o total da potência dissipada. Na realidade, a potência da corrente de fuga consegue já ultrapassar em certos casos aquela que era a principal fonte de dissipação de potência nos circuitos CMOS: a potência dinâmica, associada à transição entre estados. Para lidar com esta crescente potência da corrente de fuga, os fabricantes de circuitos equiparam os actuais processadores embebidos com vários estados de latência (sleep modes) e reduziram os custos energéticos e temporais associados a uma transição por um estado latente. Adicionalmente, há a tendência de se aumentar o número de dispositivos incluídos num único sistema embebido, devido à crescente complexidade da funcionalidade exigida às aplicações embebidas, requerendo um maior número de dispositivos de entrada-saída (I/O), traduzindo-se na prática por um aumento do consumo energético. Tal como no caso dos processadores, estes dispositivos também estão equipados com estados de latência, de forma a reduzir o consumo de energia. Um outro ponto a ter em conta relaciona-se com os problemas térmicos, devidos ao aumento da densidade de potência, presentes nos actuais processadores embebidos. É fundamental manter a temperatura dentro dos limites especificados para a operação segura do sistema e aumentar da durabilidade/fiabilidade da plataforma computacional. Por último, o paradigma de fabrico CMOS evoluiu na última década, do projecto de sistemas com um único processador para plataformas com múltiplos núcleos de execução (multi-core), pois tornou-se impossível continuar a obter ganhos de desempenho através do aumento da frequência de relógio. Esta mudança é motivada pelo aumento da relação de desempenho por watt, através de técnicas especiais de desenho dos circuitos integrados que permitem dissipar o calor gerado a altas-frequências.

Esta dissertação apresenta um conjunto de novas soluções eficientes do ponto de vista energético para lidar com as tendências previamente referidas, estabelecendo simultaneamente a ponte entre a investigação teórica e a prática. Este trabalho centra-se em particular na gestão de energia ao nível do sistema operativo, e explora os estados de latência disponíveis para melhorar a eficiência energética, concentrando-se na dissipação de potência devida às correntes de fuga. A gestão de energia em sistemas uniprocessador foi largamente explorada nas últimas duas décadas. Neste período, publicaram-se várias abordagens baseadas na procrastinação de tarefas para lidar com o problema da corrente de fuga. No entanto, estas soluções estimam um valor aproximado do intervalo de procrastinação para facilitar a análise e utilizar de forma sub-óptima os recursos disponíveis para minimizar o consumo de energia. Este trabalho conseguiu eliminar a referida

aproximação com um algoritmo óptimo para maximização da poupança de energia. A limitação prática do algoritmo de escalonamento com procrastinação de tarefas é relaxado através da eliminação da utilização de *hardware* externo para implementar o algoritmo de poupança de energia. Estes novos algoritmos de baixa complexidade, desenvolvidos neste trabalho, atingem poupanças de energia comparáveis ao escalonamento com procrastinação de tarefas. Além disso, esta dissertação demonstra como a variação dinâmica ideal de tensão e frequência, e a gestão dinâmica de consumo de potência baseada em factores térmicos são, por natureza, equivalentes. Desta forma, as actuais soluções propostas para variação dinâmica de tensão e frequência podem ser facilmente convertidas para aumentar a eficiência energética em sistemas com restrições térmicas.

O escalonamento de dispositivos de entrada-saída ao nível da tarefa tem sido negligenciado devido aos custos elevados de transições por estados de latência. A diminuição desses custos permite explorar este novo paradigma de escalonamento de dispositivos. Esta solução não só minimiza o pessimismo relacionado com os algoritmos tradicionais de escalonamento de dispositivos como também reduz os custos de execução dos algoritmos de escalonamento, possuindo a flexibilidade necessária para facilmente acompanhar um número crescente de dispositivos de entrada-saída. Por fim, esta dissertação aborda a gestão de potência no contexto das plataformas baseadas em arquitecturas de processadores com múltiplos núcleos de execução (multi-core). Os algoritmos de escalonamento globais tornaram-se uma opção interessante para ordenar a execução de tarefas em plataformas cujos múltiplos são homogéneos. O algoritmo para poupanca de energia proposto, explora a capacidade excedente do sistema decorrente do escalonamento, bem como os estados de latência disponíveis nestas plataformas de núcleos homogéneos, afim de reduzir o consumo de energia. As plataformas de núcleos heterogéneos são reconhecidas pela capacidade de realizar eficientemente tarefas específicas. Os processos de afectação de tarefas por núcleos de execução baseada em critérios de eficiência energética publicados até hoje, consideram apenas a dissipação dinâmica de potência assumindo um factor constante para a potência devida à corrente de fuga. Em oposição ao estado-da-arte actual, as heurísticas de afectação proposta nesta dissertação dividem-se em duas fases para abordar tanto a dissipação de potência dinâmica como a dissipação de potência de fuga. Todos os algoritmos propostos nesta dissertação são avaliados através de um extenso conjunto de simulações para uma variedade de plataformas computacionais submetidas a diversas cargas.

## Acknowledgements

A PhD milestone demands dedication, hard work, patience, concentration, motivation and support from people around you. Many individuals made this challenging milestone easier for me and paved the way to my success. First of all, I would like to express my very great appreciation and gratitude to my supervisor Stefan M. Petters for his valuable ideas, constructive discussions, useful feedback and excellent guidance. He never let me down at any stage and kept my motivation alive throughout my PhD process. I am very grateful to him for providing me such an exciting opportunity to work on this interesting topic, sharing his vast experience in this domain and encouraging me to work on different problems of my choice within this topic. I have learned a lot during his extraordinary supervision. I would also like to thank Eduardo Tavor for providing us an ideal research environment in CISTER. He was always accessible to solve our issues. I am also thankful to Stefan and Eduardo for arranging funds to attend conferences and summer schools. Also, I am grateful to Ines Almeida, Sanda Almeida and Cristiana Barros for taking care of administrative stuff in CISTER and Portugal. Especially, I really appreciate the effort of Ines for solving our visa-related issues and helping us with the local authorities here in Portugal. My special thanks to the technical stuff for providing us an excellent working environment in CISTER and allowing us to use lab resources for our experiments.

I would like to express my gratitude to my colleague and a good friend Patrick Meumeu Yomsi for improving my theorem proving skills and sharing interesting research ideas in the last two years of my PhD that resulted in reputed conference publications. I am extremely thankful to Geoffrey Nelissen, whose ideas on global power management and partitioned allocation problem will hopefully result in potential good quality publications. I really enjoyed working with Patrick and Goeffrey because of their clear thoughts and pragmatic approach to solve problems. My lab mate and a very good friend, Borislav Nikolic, helped me to develop the SPARTS simulator used in this thesis to evaluate the performance of different algorithms. I enjoyed his company as a friend and as a colleague. I wish to acknowledge the help of Gurulingesh Raravi and Vikram Gupta in the initial phases of my study of partitioned multicore power management problem. The discussions we had really helped me to understand the nature of the problem. I am particularly grateful to Dakai Zhu and Jian-Jia Chen for providing useful comments in the initial phases of my thesis research plan. I would also like to thank Antonio Barros, Paulo Baltarejo Sousa and Joao Loureiro for translating the abstract of my thesis to Portuguese language. I feel myself very lucky to share the workspace with Dakshina Dasari, Hazim Ali, Borislay, Artem Burmyakov and Kostiantyn Berezovskyi. You people are a great company. With such people around you never feel bored at work. Thanks to Farhan, Mushtaq, Guru, Dakshina, Anuj, Kritika, Ganga, Sujit, Shashank, Vikram, Vincent, Geoffrey, Patrick, Arif, Saqlain, Bilal, Arsalan, Ajmal and Asif for great parties, gaming nights and delicious food. These people made my PhD journey memorable.

I would not be here without a support from my family. I would like to express my deepest gratitude to my parents Altaf Hussain Awan and Shamim Akhtar for their assistance and support throughout my life. They always encouraged me to follow my dreams and avail the opportunities

in my best interest. I know it was always hard for you to stay away from me but you allowed me to leave the country for my better future. Without your support this dream of getting PhD was almost impossible. I would like to thank my sisters Tahira Naz and Farhat Yasmeen for their support, encouragement, motivation and well wishes. My special thanks to my cousin and best friend Zahid Imran for taking care of my parents in my absence. Finally, I would like to thank my dear wife Kiran Ali, who supported and motivated me throughout my PhD process. She bare with me in-spite of long working hours and mood swings. I would like to avail this opportunity to thank her for the delicious food and a great company.

This work was supported by FCT (Portuguese Foundation for Science and Technology) and by ESF (European Social Fund) through POPH (Portuguese Human Potential Operational Program), under PhD grant SFRH/BD/70701/2010..

Muhammad Ali Awan

"Education is not the learning of facts, but the training of the mind to think."

Albert Einstein

# **Contents**

| 1 | Intr | roduction                                                                     | 1          |

|---|------|-------------------------------------------------------------------------------|------------|

|   | 1.1  | Embedded Systems                                                              | 1          |

|   | 1.2  | Basic Components of Real-Time Systems                                         | 5          |

|   |      | 1.2.1 Applications                                                            | 5          |

|   |      | 1.2.2 Real-Time Operating System                                              | 7          |

|   |      | 1.2.3 Hardware Platform                                                       | 11         |

|   | 1.3  | Power Saving Techniques                                                       | 18         |

|   |      | 1.3.1 Dynamic Power Management                                                | 19         |

|   |      |                                                                               | 20         |

|   | 1.4  | Current Trends in Embedded Systems and their Impact on Energy Consumption . 2 | 21         |

|   |      | 1.4.1 Non-negligible leakage-power Dissipation                                | 21         |

|   |      |                                                                               | 22         |

|   |      |                                                                               | 23         |

|   |      | 1.4.4 Towards Multicore                                                       | 23         |

|   |      | 1.4.5 Mixed Criticality                                                       | 23         |

|   | 1.5  | Thesis Statement                                                              | 23         |

|   | 1.6  | Focus of this Dissertation                                                    | 24         |

|   | 1.7  | Thesis Organisation                                                           | 25         |

|   | 1.8  | Published Research in the Context of this Dissertation                        | 26         |

|   |      | 1.8.1 Conference Publications                                                 | 26         |

|   |      | 1.8.2 Journals                                                                | 28         |

|   |      | 1.8.3 Workshops, Posters and Work-in-Progress                                 | 29         |

| 2 | Stat | te of the art                                                                 | 31         |

|   | 2.1  | Unicore Power Management                                                      | 31         |

|   |      |                                                                               | 31         |

|   |      |                                                                               | 33         |

|   |      |                                                                               | 36         |

|   | 2.2  |                                                                               | 37         |

|   |      |                                                                               | 37         |

|   |      | · · · · · · · · · · · · · · · · · · ·                                         | 39         |

| 3 | Mod  | del of Computation and Simulation Framework                                   | <b>1</b> 1 |

|   | 3.1  | 1                                                                             | 11         |

|   |      | * *                                                                           | 11         |

|   |      |                                                                               | 12         |

|   |      | <b>r</b>                                                                      | 13         |

|   |      |                                                                               | 15         |

X CONTENTS

|   |            | 3.1.5    | Slack Management Algorithm                                              | . 46    |

|---|------------|----------|-------------------------------------------------------------------------|---------|

|   | 3.2        | Simula   | ation Framework                                                         | . 48    |

| 4 | Unio       | core Pov | wer Management                                                          | 51      |

|   | 4.1        |          | stination Scheduling                                                    | . 52    |

|   |            | 4.1.1    | Basics                                                                  |         |

|   |            | 4.1.2    | Demand Bound Function Based Procrastination (DBFP)                      | . 55    |

|   |            | 4.1.3    | Analytical Analysis of Procrastination Interval of each Task            | . 58    |

|   |            | 4.1.4    | Improvements in Minimum Idle interval (Static Sleep Interval)           | . 60    |

|   |            | 4.1.5    | Extending DBFP to the Constrained Deadline Task Model and its Optima    | lity 65 |

|   | 4.2        | Altern   | ative Real-Time Race-To-Halt Algorithms                                 | . 66    |

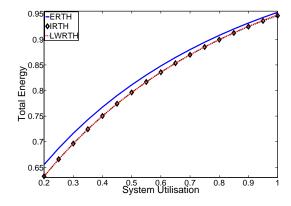

|   |            | 4.2.1    | Enhanced Race-To-Halt Algorithm (ERTH)                                  | . 67    |

|   |            | 4.2.2    | Improved Race-To-Halt Algorithm (IRTH)                                  |         |

|   |            | 4.2.3    | Light-Weight Race-To-Halt Algorithm (LWRTH)                             |         |

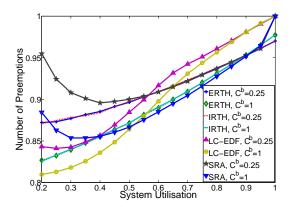

|   | 4.3        | Effect   | of Sleep-States on the Number of Pre-emptions                           | . 77    |

|   | 4.4        | Evalua   | ation of CPU Power Management Algorithms                                | . 78    |

|   |            | 4.4.1    | Overhead Analysis                                                       |         |

|   |            | 4.4.2    | Simulation Results of the DBFP Algorithm                                |         |

|   |            | 4.4.3    | Simulation Results of ERTH, IRTH and LWRTH Algorithms                   |         |

|   |            | 4.4.4    | Pre-emptions Related Results                                            |         |

|   | 4.5        |          | al-Aware Energy Management                                              |         |

|   |            | 4.5.1    | Extension in the System Model                                           |         |

|   |            | 4.5.2    | Preliminaries                                                           |         |

|   |            | 4.5.3    | Equivalence of Idealised DVFS and TCDPM                                 |         |

|   |            | 4.5.4    | Case Study                                                              |         |

|   |            | 4.5.5    | Implementation Concerns                                                 |         |

|   | 4.6        | Evalua   | ation of Thermal-Aware Energy Management Approach                       | . 103   |

| 5 | Devi       | ice Pow  | er Management                                                           | 109     |

|   | 5.1        | Prelim   | inaries                                                                 | . 110   |

|   | 5.2        | A Sing   | gle Sleep State per Device Model                                        |         |

|   |            | 5.2.1    | Static Slack Container Algorithm (SSC)                                  |         |

|   | 5.3        |          | e Budget Reclamation                                                    |         |

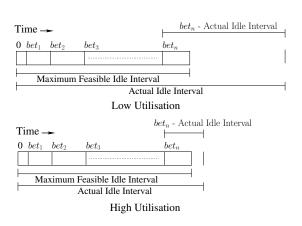

|   |            | 5.3.1    | Terminologies and Basic Idea                                            |         |

|   |            | 5.3.2    | Sources to Reclaim Device Budget                                        |         |

|   |            | 5.3.3    | Device Budget Reclamation Algorithm                                     |         |

|   | 5.4        | _        | ble Sleep States Per Device Model                                       |         |

|   |            | 5.4.1    | Base Idea                                                               |         |

|   |            | 5.4.2    | Energy-Density Function                                                 |         |

|   |            | 5.4.3    | Devices and their Sleep State Categorisation                            |         |

|   |            | 5.4.4    | Offline Algorithm for Multiple Sleep State Devices (SSC <sup>o</sup> )  |         |

|   |            | 5.4.5    | Static Slack Container Algorithm with Multiple Sleep State Devices (SSO |         |

|   |            | 5.4.6    | Aggressive Static Slack Container Algorithm for Multiple Sleep State De |         |

|   | <i>-</i> - | ъ.       | vices (SSC <sup>a</sup> )                                               |         |

|   | 5.5        |          | ation of Device Power Management Algorithms                             |         |

|   |            | 5.5.1    | Complexity Comparison                                                   |         |

|   |            | 5.5.2    | Experimental Setup                                                      |         |

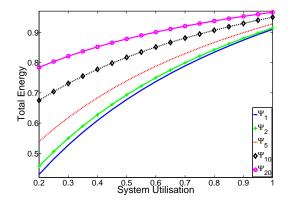

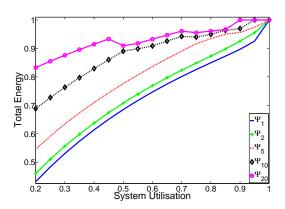

|   |            | 5.5.3    | Simulation Results of a Single Sleep State Devices Model                |         |

|   |            | 5.5.4    | Simulation Results of the Multiple Sleep State Devices Model            | . 136   |

*CONTENTS* xi

| 6 | Glol | oal Scheduler | and Power Management                              |      |   | 141   |

|---|------|---------------|---------------------------------------------------|------|---|-------|

|   | 6.1  | Preliminaries | 8                                                 | <br> |   | . 142 |

|   |      | 6.1.1 Exter   | nsions in the System Model                        | <br> |   | . 142 |

|   |      | 6.1.2 Expe    | ected Release Time                                | <br> |   | . 143 |

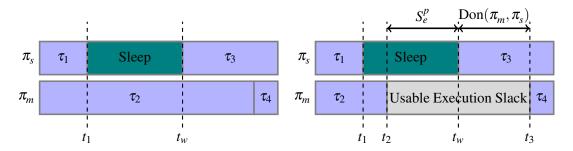

|   |      | 6.1.3 Usab    | ole Execution Slack                               | <br> |   | . 143 |

|   |      |               | ole Idle Slack                                    |      |   |       |

|   | 6.2  |               | ergy Saving Algorithm                             |      |   |       |

|   |      | •             | oiting the Usable Execution Slack                 |      |   |       |

|   |      | _             | oiting the Usable Idle Slack                      |      |   |       |

|   |      | 1             | rithmic Summary                                   |      |   |       |

|   | 6.3  | Proof of Corr |                                                   |      |   |       |

|   | 6.4  | Evaluation of | f Global Power Management Algorithm               |      |   |       |

|   |      |               | erimental Setup                                   |      |   |       |

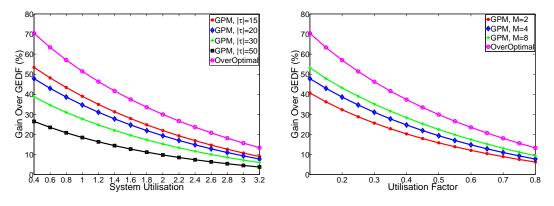

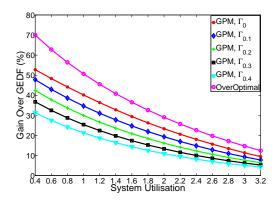

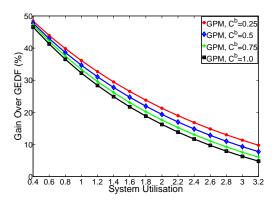

|   |      |               | alation Results of the GPM Algorithm              |      |   |       |

| _ | _    |               |                                                   |      |   |       |

| 7 |      |               | core Power Management                             |      |   | 157   |

|   | 7.1  |               | n the System Model                                |      |   |       |

|   |      |               | ware Platform                                     |      |   |       |

|   |      |               | Model                                             |      |   |       |

|   | 7.0  |               | er Model                                          |      |   |       |

|   | 7.2  |               | euristics (Non-DVFS)                              |      |   |       |

|   |      |               | Phase of Allocation                               |      |   |       |

|   | 7.2  |               | nd Phase of Optimisation                          |      |   |       |

|   | 7.3  |               | euristics (With DVFS)                             |      |   |       |

|   |      |               | Phase of Allocation                               |      |   |       |

|   | 7.4  |               | nd Phase of Optimisation                          |      |   |       |

|   | 7.4  |               | f the Partitioned Multicore Allocation Heuristics |      |   |       |

|   |      |               | nlation Results (Non-DVFS)                        |      |   |       |

|   |      | 7.4.2 Simu    | alation Results (With DVFS)                       | <br> | • | . 183 |

| 8 |      |               | spective and Future Directions                    |      |   | 191   |

|   | 8.1  | •             | the Work                                          |      |   |       |

|   |      |               | ore Power Management                              |      |   |       |

|   |      |               | ce Power Management                               |      |   |       |

|   |      |               | icore Power Management with Global Scheduling     |      |   |       |

|   |      |               | tioned Multicore Power Management                 |      |   |       |

|   | 8.2  |               | and Future Directions                             |      |   |       |

|   |      | •             | endent Task Model                                 |      |   |       |

|   |      |               | ce Power Management                               |      |   |       |

|   |      |               | icore Power Management                            |      |   |       |

|   |      |               | sive Multicore Power Management                   |      |   |       |

|   | 8.3  | End Note .    |                                                   | <br> | • | . 196 |

| A | Eval | uation of CPI | U Power Management Algorithms                     |      |   | 197   |

|   | A.1  | Overhead An   | •                                                 |      |   |       |

|   |      |               | plexity of LC-EDF                                 |      |   |       |

|   |      | A.1.2 Comp    | plexity of PROC and DBFP                          | <br> |   | . 197 |

|   |      | A.1.3 Comp    | plexity of ERTH                                   | <br> |   | . 198 |

|   |      | A 1 4 Com     | plexity of IRTH                                   |      |   | . 198 |

xii CONTENTS

|     | A.1.5  | Complexity of LWRTH                                                      | 199 |

|-----|--------|--------------------------------------------------------------------------|-----|

| A.2 | Simula | ation Results of the DBFP Algorithm                                      | 200 |

|     | A.2.1  | Experimental Setup                                                       | 200 |

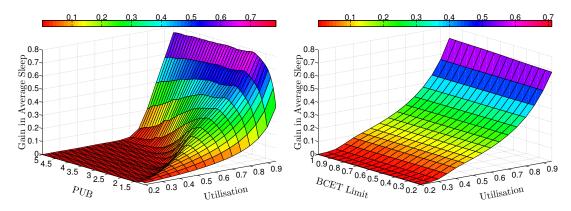

|     | A.2.2  | Analysing Average Sleep Interval                                         | 201 |

|     |        | Analysing Reducible Energy Consumption                                   | 202 |

| A.3 | Simula | ation Results of ERTH, IRTH and LWRTH Algorithms                         | 203 |

|     | A.3.1  | Experimental Setup                                                       | 203 |

|     | A.3.2  | Scenario 1 ( $A_i = C_i$ , $\forall$ task types)                         | 204 |

|     | A.3.3  | Scenario 2 $(RT \Rightarrow (A_i = C_i), BE \Rightarrow (A_i \leq C_i))$ | 213 |

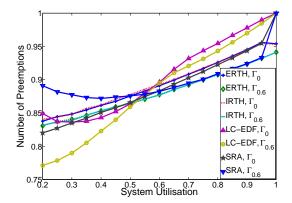

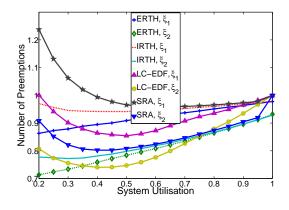

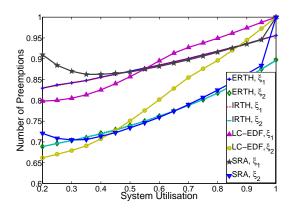

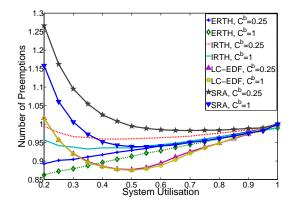

| A.4 | Pre-en | nptions Related Results                                                  | 215 |

|     | A.4.1  | Scenario 1                                                               | 216 |

|     | A.4.2  | Scenario 2                                                               | 219 |

# **List of Figures**

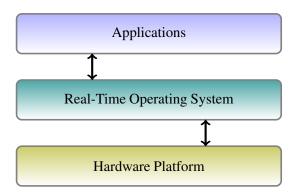

| 1.1  | Different components of a RT system                                                                                                                                  | 5   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

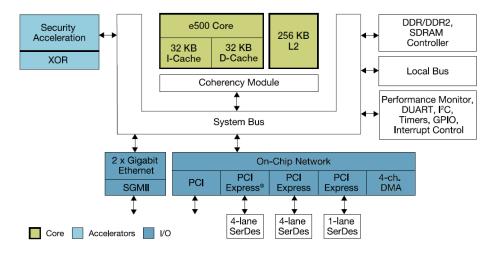

| 1.2  | Block diagram of MPC8544E PowerQUICC III processor (source [Fre14])                                                                                                  | 12  |

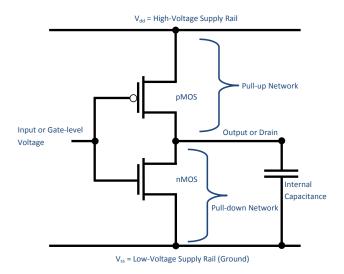

| 1.3  | CMOS NOT logic gate (input-inverter)                                                                                                                                 | 15  |

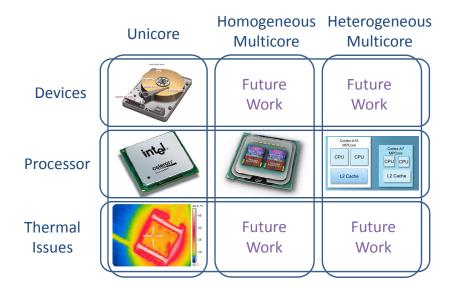

| 1.4  | Highlighting the focus of this dissertation                                                                                                                          | 24  |

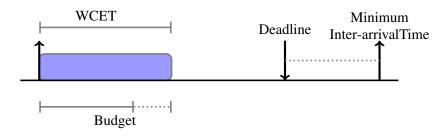

| 3.1  | Task specifications                                                                                                                                                  | 41  |

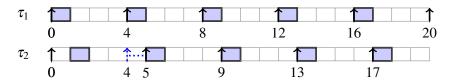

| 3.2  | Sporadic slack example                                                                                                                                               | 45  |

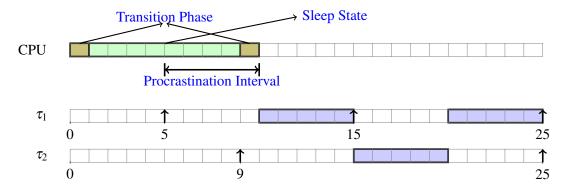

| 4.1  | Schedule with $\tau_1 = \langle 5, 10, 10 \rangle$ , $\tau_2 = \langle 5, 16, 16 \rangle$ and $tr_n = 1 \dots \dots \dots \dots$                                     | 52  |

| 4.2  | "Accumulated delays under EDF scheduling [LRK03]"                                                                                                                    | 53  |

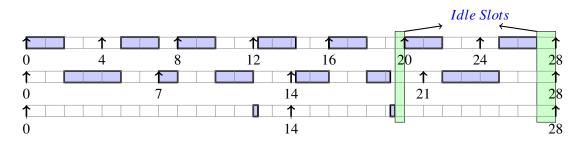

| 4.3  | Schedule with $\tau_1 = \langle 2, 4, 4 \rangle, \tau_2 = \langle 3, 7, 7 \rangle$ and $\tau_3 = \langle 0.25, 14, 14 \rangle$                                       | 55  |

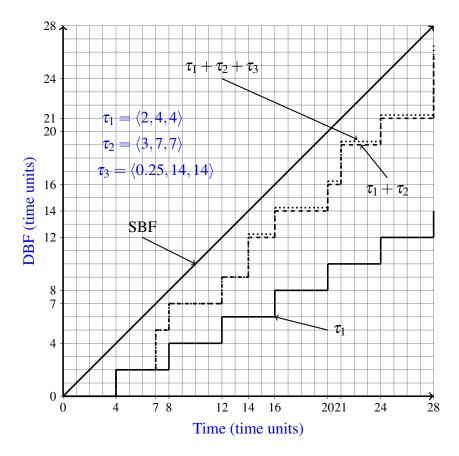

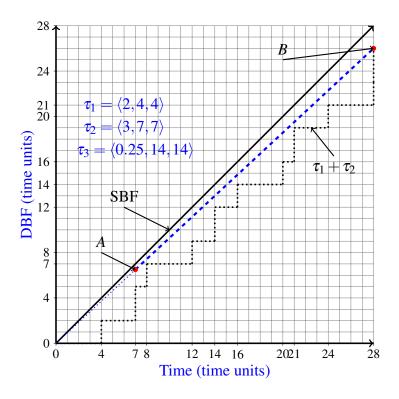

| 4.4  | Demand bound function with tasks $\tau_1 = \langle 2, 4, 4 \rangle$ , $\tau_2 = \langle 3, 7, 7 \rangle$ and $\tau_3 = \langle 0.25, 14, 14 \rangle$                 | 56  |

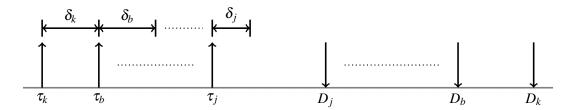

| 4.5  | Procrastination interval for $\tau_2$                                                                                                                                | 59  |

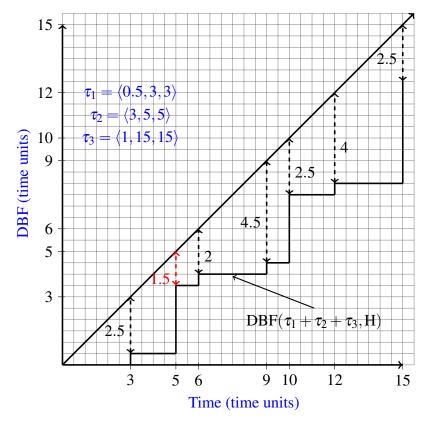

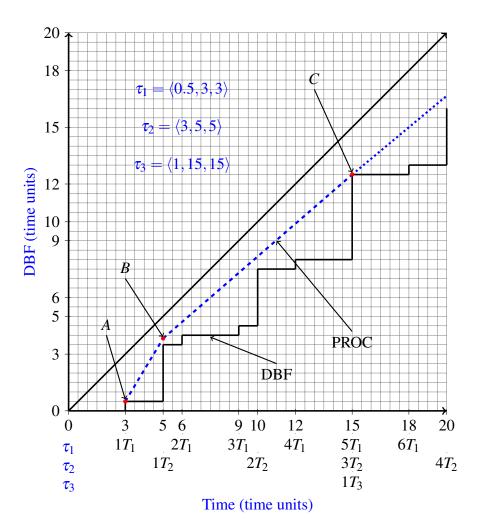

| 4.6  | Static sleep interval with tasks $\tau_1 = \langle 0.5, 3, 3 \rangle$ , $\tau_2 = \langle 3, 5, 5 \rangle$ and $\tau_3 = \langle 1, 15, 15 \rangle$ .                | 61  |

| 4.7  | DBF vs SRA                                                                                                                                                           | 63  |

| 4.8  | Example to illustrate that $\varphi \geq \chi_{min}$ with a task-set composed of $\tau_1 = \langle 2, 8, 8 \rangle$ ,                                                |     |

|      | $\tau_2 = \langle 1, 9, 9 \rangle, \ \tau_3 = \langle 5, 12, 12 \rangle, \ \tau_4 = \langle 3, 14, 14 \rangle \ \text{and} \ \chi_{min} = 1 \dots \dots \dots \dots$ | 71  |

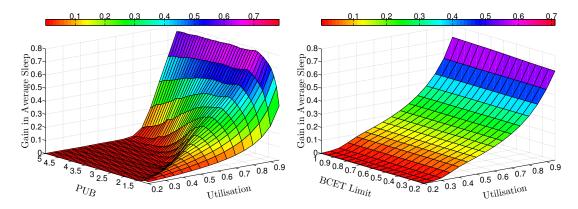

| 4.9  | Variation in $T_{max}$ (sleep interval)                                                                                                                              | 82  |

| 4.10 | Variation in $C^b$ (sleep interval)                                                                                                                                  | 82  |

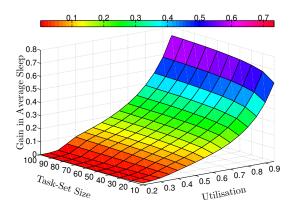

| 4.11 | Variation in $ \tau $ (sleep interval)                                                                                                                               | 82  |

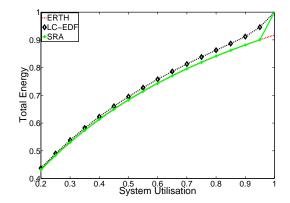

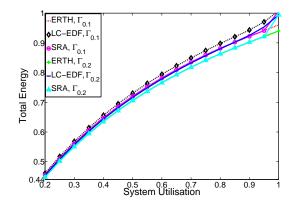

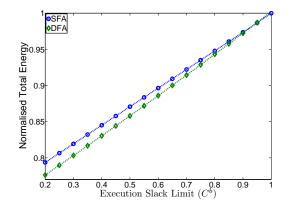

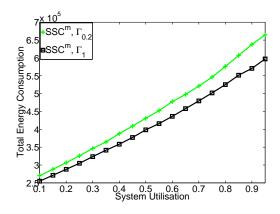

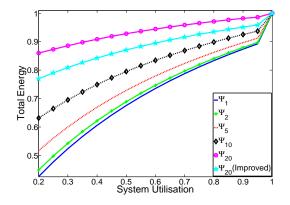

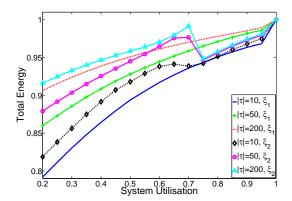

| 4.12 | Normalised total energy consumption ( $\xi_1$ and $ \tau  = 200$ )                                                                                                   | 84  |

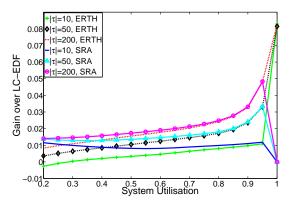

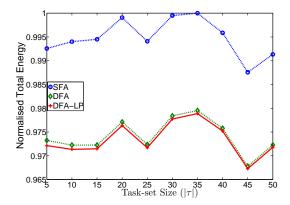

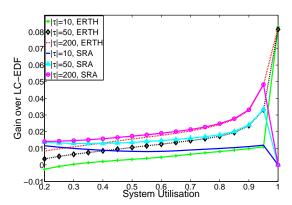

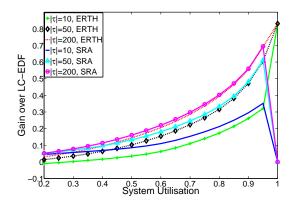

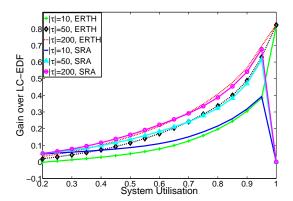

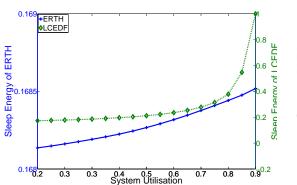

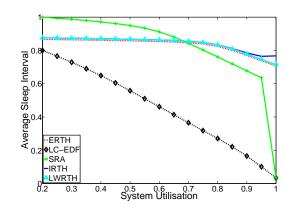

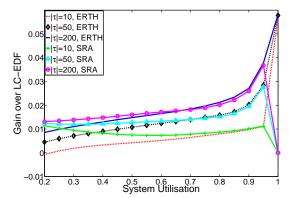

| 4.13 | Gain of ERTH and SRA over LC-EDF for different task-set sizes                                                                                                        | 84  |

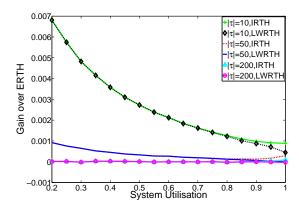

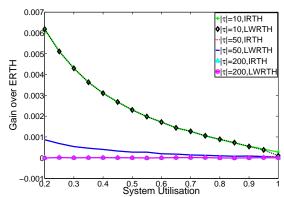

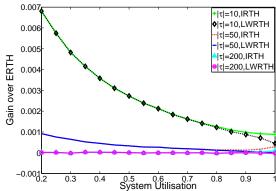

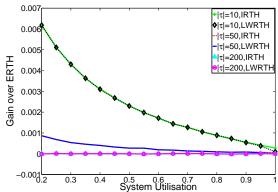

|      | Overall-gain of IRTH and LWRTH over ERTH $(\xi_1)$                                                                                                                   | 85  |

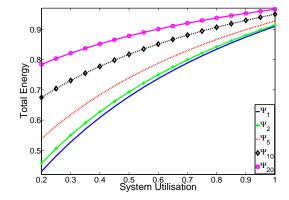

| 4.15 | Sleep threshold effect on total energy of ERTH ( $ \tau  = 50$ and $\xi_1$ )                                                                                         | 85  |

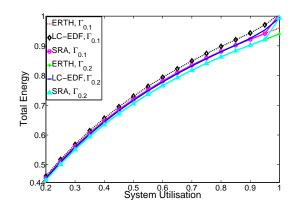

| 4.16 | Normalised total energy consumption with $ \tau  = 200$ and $\xi_1$                                                                                                  | 86  |

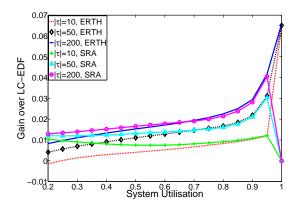

| 4.17 | Overall-gain of IRTH and LWRTH over ERTH ( $\xi_1$ and $\Gamma_{0.1}$ )                                                                                              | 86  |

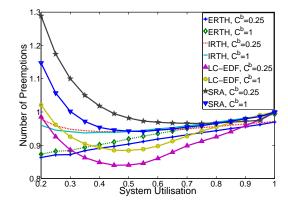

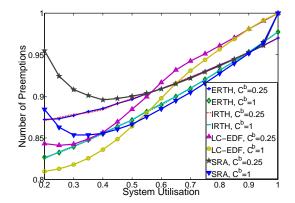

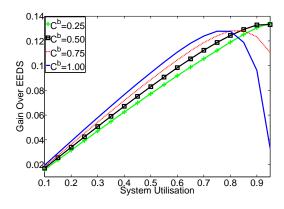

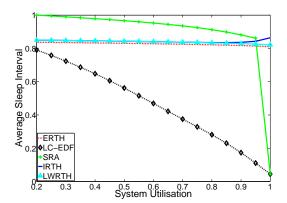

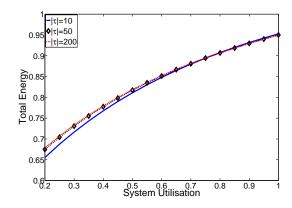

| 4.18 | Variation in $C^b$ for $ \tau  = 10$ $(\Gamma_{0.2}, \xi_1)$                                                                                                         | 88  |

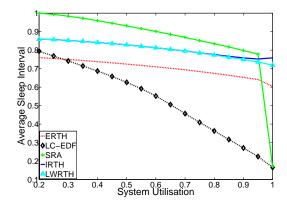

| 4.19 | Variation in $C^b$ for $ \tau  = 50$ $(\Gamma_{0.2}, \xi_1)$                                                                                                         | 88  |

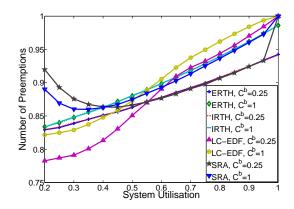

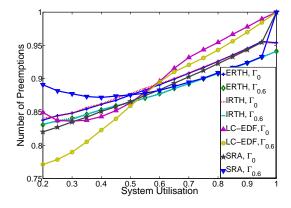

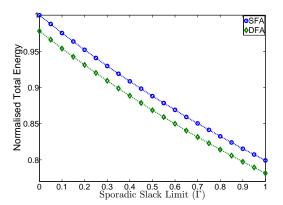

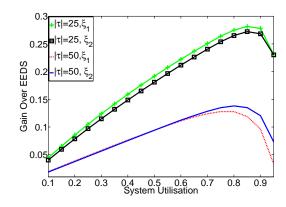

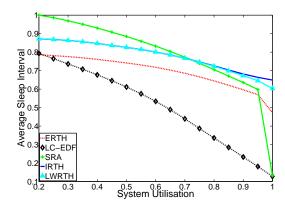

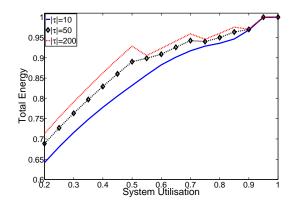

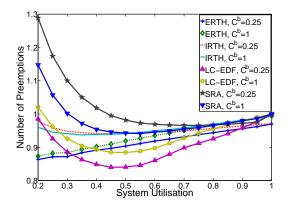

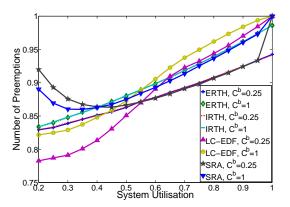

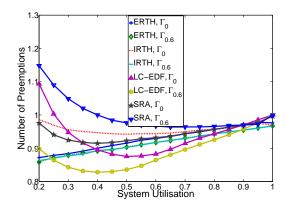

|      | Variation in $\Gamma$ for $ \tau  = 50 (\xi_1) \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                | 89  |

|      | Variation in $C^b$ in scenario 2 for $ \tau  = 50 \ (\Gamma_{0.2}, \xi_1)$                                                                                           | 89  |

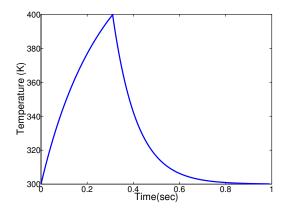

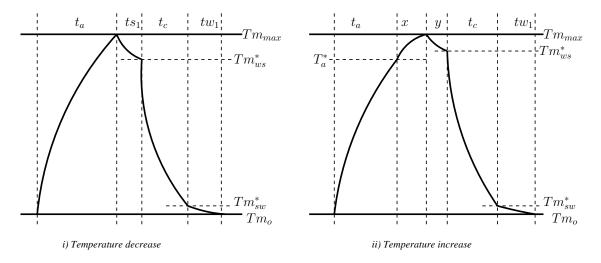

| 4.22 | Temperature profile                                                                                                                                                  | 95  |

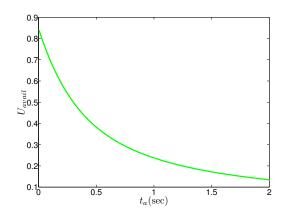

|      | $U_{avail}$ vs $t_a$                                                                                                                                                 | 95  |

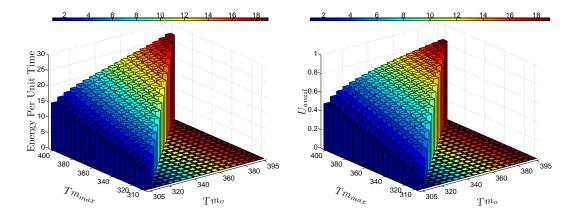

|      | Energy vs operating temperature range                                                                                                                                | 96  |

| 4.25 | $U_{avail}$ vs operating temperature range                                                                                                                           | 96  |

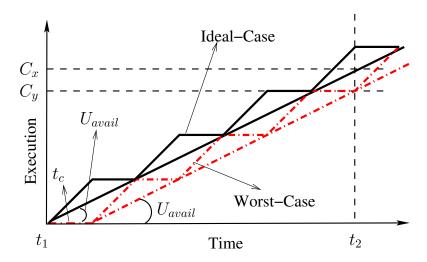

|      | Service curve                                                                                                                                                        | 98  |

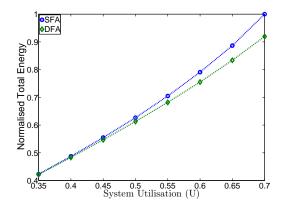

|      |                                                                                                                                                                      | 103 |

| 4.28 | Variation in system utilisation                                                                                                                                      | 105 |

|      |                                                                                                                                                                      | 105 |

xiv LIST OF FIGURES

| 4.30       | Variation in number of tasks                                                                                                                | 106  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.31       | Variation in sporadic slack                                                                                                                 | 106  |

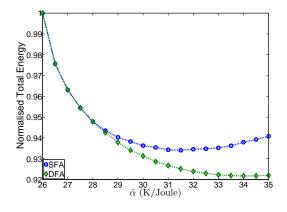

| 4.32       | Variation in $\hat{\alpha}$                                                                                                                 | 107  |

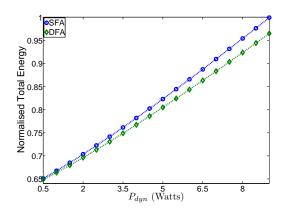

| 4.33       | Variation in $P_{dyn}$                                                                                                                      | 107  |

|            | · · · · · · · · · · · · · · · · · · ·                                                                                                       | 108  |

|            | •                                                                                                                                           |      |

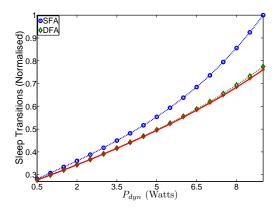

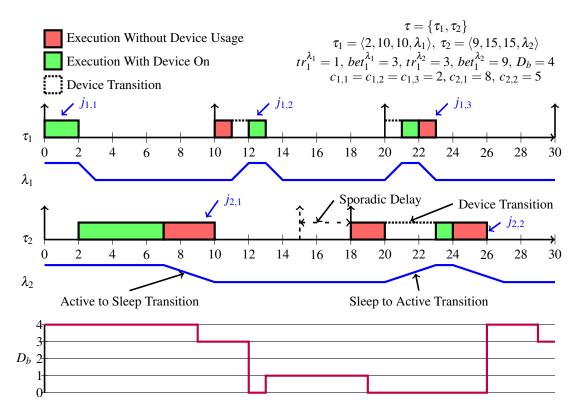

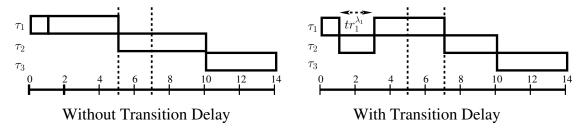

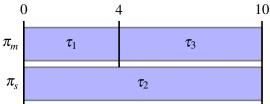

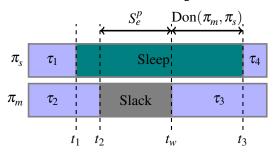

| 5.1        | Example with two tasks $(\tau_1 = \langle 2, 10, 10, \lambda_1 \rangle, \ \tau_2 = \langle 9, 15, 15, \lambda_2 \rangle) \dots \dots \dots$ | 112  |

| 5.2        | Low priority workload overlap                                                                                                               | 120  |

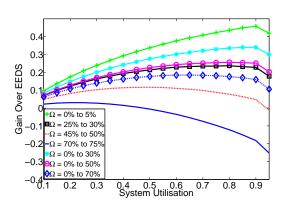

| 5.3        | Variation in $\Omega$                                                                                                                       | 133  |

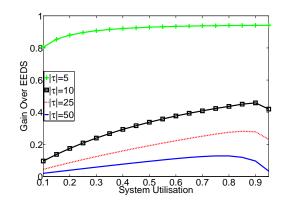

| 5.4        | Variation in $ \tau $ against $U$                                                                                                           | 133  |

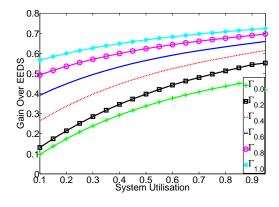

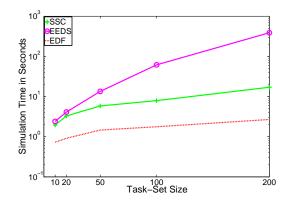

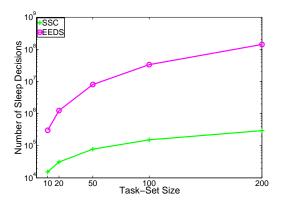

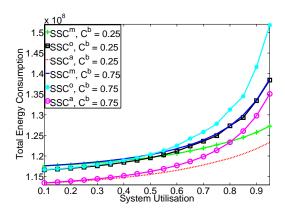

| 5.5        |                                                                                                                                             | 134  |

| 5.6        |                                                                                                                                             | 134  |

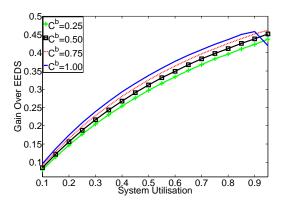

| 5.7        |                                                                                                                                             | 135  |

| 5.8        |                                                                                                                                             | 135  |

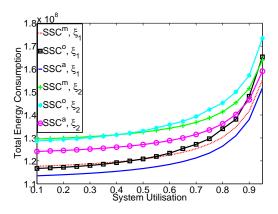

| 5.9        |                                                                                                                                             | 136  |

| 5.10       | •                                                                                                                                           | 136  |

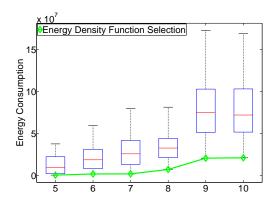

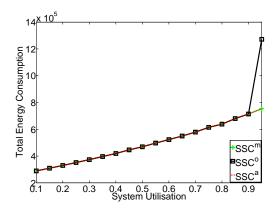

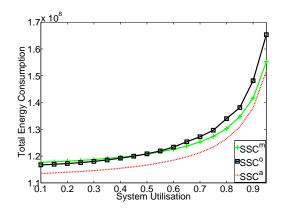

|            | * ED *                                                                                                                                      | 137  |

|            |                                                                                                                                             | 137  |

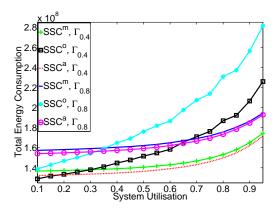

|            |                                                                                                                                             | 137  |

|            |                                                                                                                                             | 138  |

|            | 11 1                                                                                                                                        | 139  |

|            | N I /                                                                                                                                       |      |

|            |                                                                                                                                             | 139  |

| 5.17       | Variation in $\xi$ ( $ \tau  = 50$ )                                                                                                        | 139  |

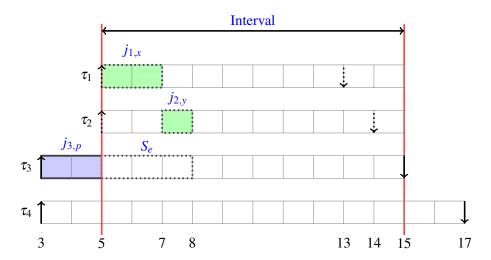

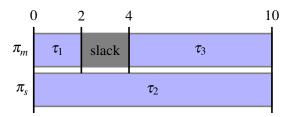

| 6.1        | Initial schedule when all tasks execute for their WCET                                                                                      | 146  |

| 6.2        |                                                                                                                                             | 146  |

| 6.3        |                                                                                                                                             | 146  |

| 6.4        |                                                                                                                                             | 146  |

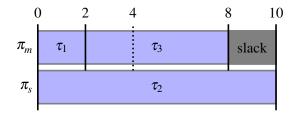

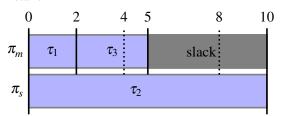

| 6.5        | •                                                                                                                                           | 140  |

|            |                                                                                                                                             |      |

| 6.6        | 2 1 2                                                                                                                                       | 147  |

| 6.7        | m s                                                                                                                                         | 147  |

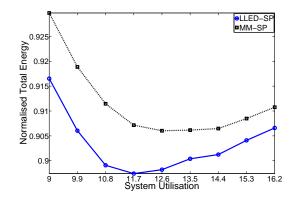

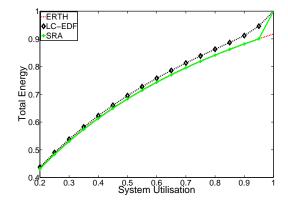

| 6.8        |                                                                                                                                             | 153  |

| 6.9        |                                                                                                                                             | 153  |

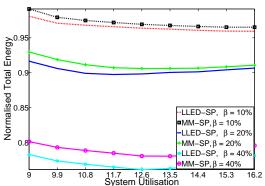

|            |                                                                                                                                             | 154  |

|            |                                                                                                                                             | 154  |

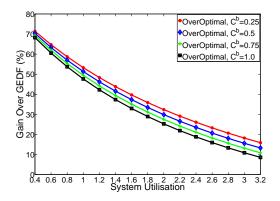

| 6.12       | Variation in $C^b$ (OverOptimal)                                                                                                            | 155  |

| <b>7</b> 1 |                                                                                                                                             | 1.00 |

| 7.1        |                                                                                                                                             | 163  |

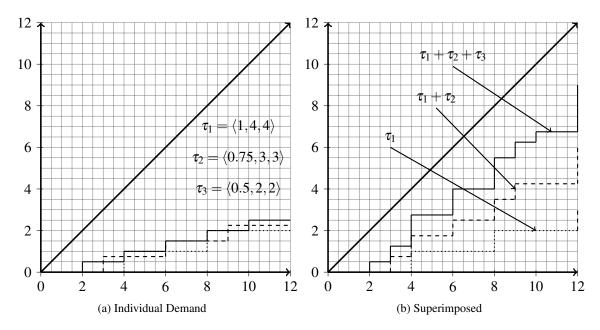

| 7.2        | Demand bound function to demonstrate the computation of static sleep interval set                                                           |      |

|            | in the second phase of optimisation with tasks $\tau_1 = \langle 1, 4, 4 \rangle, \tau_2 = \langle 0.75, 3, 3 \rangle$ and                  |      |

|            |                                                                                                                                             | 166  |

| 7.3        | · / / / / / / / / / / / / / / / / / / /                                                                                                     | 178  |

| 7.4        |                                                                                                                                             | 178  |

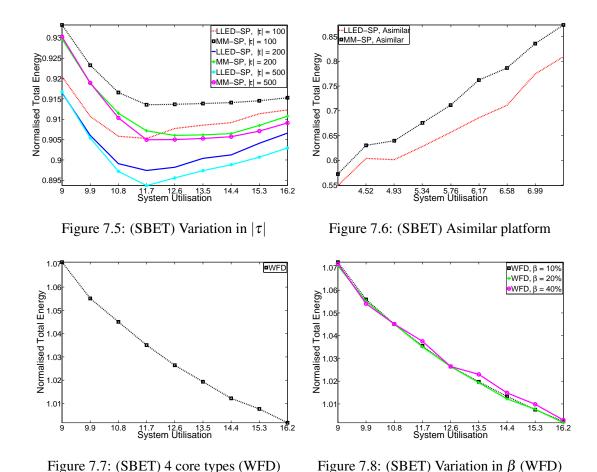

| 7.5        |                                                                                                                                             | 179  |

| 7.6        | ·                                                                                                                                           | 179  |

| 7.7        |                                                                                                                                             | 179  |

| 7.8        | (SBET) Variation in $\beta$ (WFD)                                                                                                           | 179  |

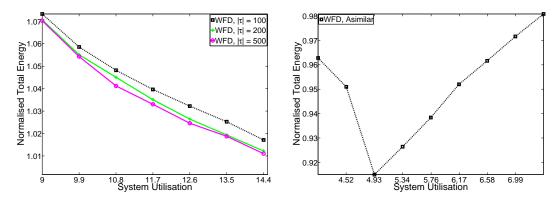

| 7.9        | (SBET) Variation in $ \tau $ (WFD)                                                                                                          | 180  |

| 7.10       | (SBET) Asimilar platform (WFD)                                                                                                              | 180  |

LIST OF FIGURES xv

|             | (* P.777), 4                                                                           | 404 |

|-------------|----------------------------------------------------------------------------------------|-----|

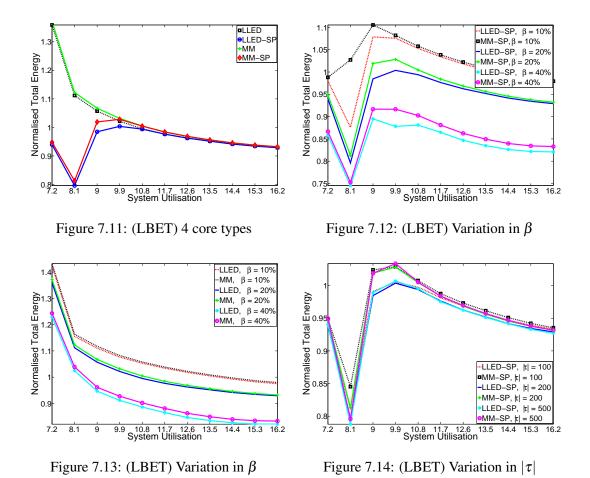

|             | (LBET) 4 core types                                                                    | 181 |

|             | (LBET) Variation in $\beta$                                                            | 181 |

|             | (LBET) Variation in $\beta$                                                            | 181 |

|             | (LBET) Variation in $ \tau $                                                           | 181 |

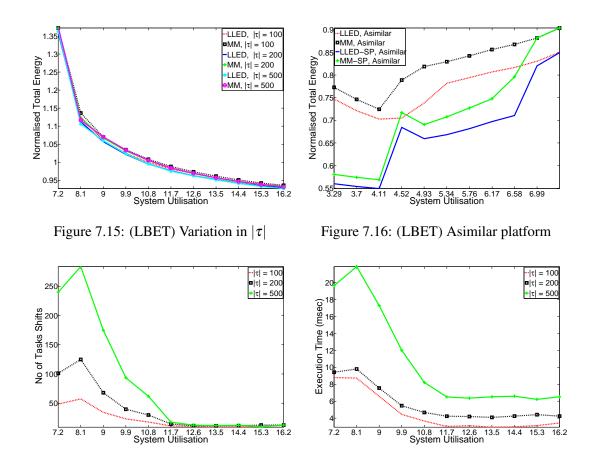

|             | (LBET) Variation in $ \tau $                                                           | 182 |

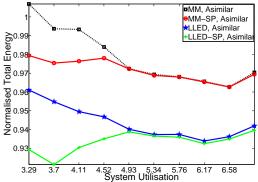

|             | (LBET) Asimilar platform                                                               | 182 |

|             | (LBET) Decisions                                                                       | 182 |

| 7.18        | (LBET) Time calculation                                                                | 182 |

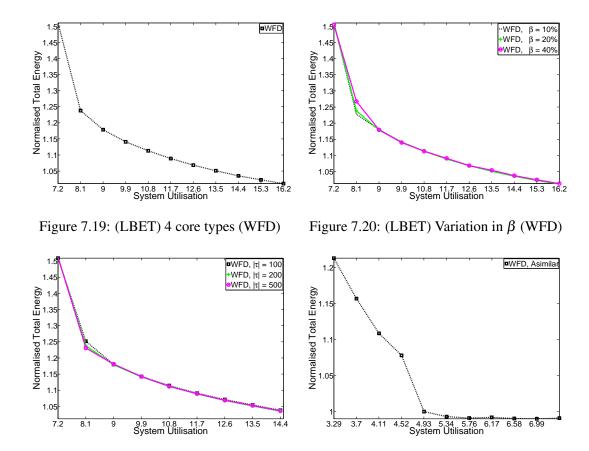

|             | (LBET) 4 core types (WFD)                                                              | 183 |

| 7.20        | (LBET) Variation in $\beta$ (WFD)                                                      | 183 |

|             | (LBET) Variation in $ \tau $ (WFD)                                                     | 183 |

|             | (LBET) Asimilar platform (WFD)                                                         | 183 |

| 7.23        | Latency hiding instruction scaling                                                     | 185 |

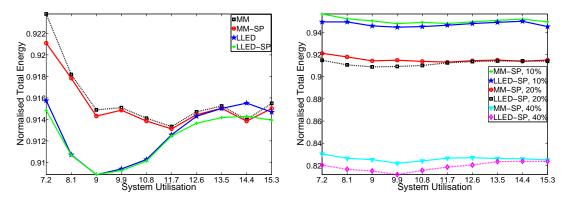

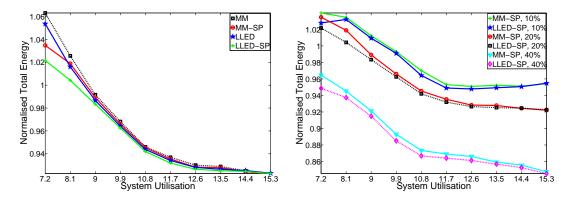

| 7.24        | (SBET) 4 core types                                                                    | 186 |

| 7.25        | (SBET) Variation in $\beta$                                                            | 186 |

| 7.26        | (SBET) Variation in $ \tau $                                                           | 187 |

|             | (SBET) Asimilar platform                                                               | 187 |

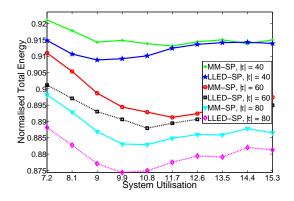

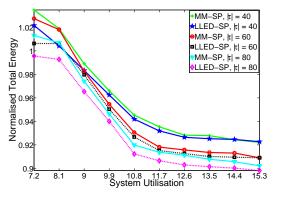

| 7.28        | (LBET) 4 core types                                                                    | 188 |

| 7.29        | (LBET) Variation in $\beta$                                                            | 188 |

| 7.30        | (LBET) Variation in $ \tau $                                                           | 189 |

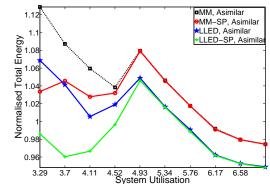

|             | (LBET) Asimilar platform                                                               | 189 |

|             |                                                                                        |     |

| <b>A.</b> 1 | Variation in $T_{max}$ (sleep interval)                                                | 201 |

| A.2         | Variation in $C^b$ (sleep interval)                                                    | 201 |

| A.3         | Variation in $ \tau $ (sleep interval)                                                 | 202 |

| A.4         | Variation in $T_{max}$ (REC)                                                           | 202 |

| A.5         | Variation in $C^b$ (REC)                                                               | 202 |

| A.6         | Variation in $ \tau $ (REC)                                                            | 202 |

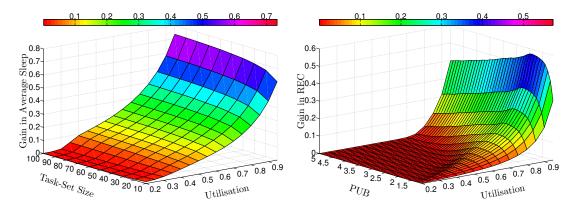

| A.7         | Normalised total energy consumption ( $\xi_1$ and $ \tau  = 200$ )                     | 204 |

| A.8         | Gain of ERTH and SRA over LC-EDF for different task-set sizes                          | 204 |

| A.9         | Gain of ERTH and SRA over LC-EDF in idle interval $(\xi_1)$                            | 206 |

|             | Gain of ERTH and SRA over LC-EDF in idle interval $(\xi_2)$                            | 206 |

|             | Normalised sleep energy consumption ( $\xi_1$ and $ \tau  = 200$ )                     | 207 |

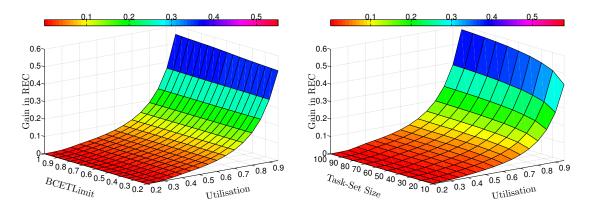

| A.12        | Overall-gain of IRTH and LWRTH over ERTH $(\xi_1)$                                     | 207 |

| A.13        | Normalised average sleep interval ( $ \tau =10$ and $\xi_1$ )                          | 208 |

| A.14        | Normalised average sleep interval ( $ \tau  = 50$ and $\xi_1$ )                        | 208 |

| A.15        | Normalised average sleep interval ( $ \tau =10$ and $\xi_2$ )                          | 209 |

| A.16        | Normalised average sleep interval ( $ \tau  = 50$ and $\xi_2$ )                        | 209 |

| A.17        | Effect of sleep threshold change on total energy consumption of ERTH ( $ \tau  = 50$   |     |

|             | and $\xi_1$ )                                                                          | 210 |

| A.18        | Effect of sleep threshold change on total energy consumption of LC-EDF ( $ \tau  = 50$ |     |

|             | and $\xi_1$ )                                                                          | 210 |

| A.19        | Energy drop on same threshold of the LC-EDF algorithm                                  | 210 |

| A.20        | Effect of sleep threshold change on total energy consumption of SRA ( $ \tau  = 50$    |     |

|             | and $\xi_1)$                                                                           | 210 |

| A.21        | Effect of sleep threshold $\Psi_{10}$ on ERTH $(\xi_1)$                                | 211 |

|             | Effect of sleep threshold $\Psi_{10}$ on LC-EDF $(\xi_1)$                              | 211 |

|             | Total energy consumption of ERTH, IRTH and LWRTH at $\Psi_{10}$ with $ \tau =10$ and   |     |

|             | $\xi_1$                                                                                | 212 |

xvi LIST OF FIGURES

| A.24 | Effect of two different distributions ( $\xi_1, \xi_2$ ) on high sleep threshold ( $\Psi_{20}$ ) with the |     |

|------|-----------------------------------------------------------------------------------------------------------|-----|

|      | SRA algorithm                                                                                             | 212 |

| A.25 | Normalised total energy consumption with $ \tau  = 200$ and $\xi_1$                                       | 213 |

| A.26 | Overall-gain of ERTH and SRA over LC-EDF ( $\xi_2$ and $\Gamma_{0.1}$ )                                   | 213 |

| A.27 | Overall-gain of ERTH and SRA over LC-EDF ( $\xi_2$ and $\Gamma_{0.2}$ )                                   | 214 |

| A.28 | Overall-gain of IRTH and LWRTH over ERTH ( $\xi_1$ and $\Gamma_{0.1}$ )                                   | 214 |

| A.29 | Variation in $C^b$ for $ \tau  = 10$ $(\Gamma_{0.2}, \xi_1)$                                              | 216 |

| A.30 | Variation in $C^b$ for $ \tau  = 50$ $(\Gamma_{0.2}, \xi_1)$                                              | 216 |

| A.31 | Variation in $\Gamma$ for $ \tau =10$ $(\xi_1)$                                                           | 218 |

| A.32 | Variation in $\Gamma$ for $ \tau =50$ $(\xi_1)$                                                           | 218 |

| A.33 | Variation in $\xi$ for $ \tau  = 10$ ( $\Gamma_{0.2}$ , $C^b = 0.5$ )                                     | 219 |

| A.34 | Variation in $\xi$ for $ \tau  = 50$ ( $\Gamma_{0.2}$ , $C^b = 0.5$ )                                     | 219 |

| A.35 | Variation in $C^b$ for $ \tau  = 10$ $(\Gamma_{0.2}, \xi_1)$                                              | 220 |

| A.36 | Variation in $C^b$ for $ \tau  = 50 (\Gamma_{0.2}, \xi_1)$                                                | 220 |

# **List of Tables**

| Overview of simulator parameters used to evaluate demand bound function based           |                 |

|-----------------------------------------------------------------------------------------|-----------------|

| procrastination                                                                         | 80              |

| Different sleep states parameters                                                       | 81              |

|                                                                                         | 83              |

| Overview of simulator parameters used to evaluate thermal-aware energy manage-          |                 |

|                                                                                         | 04              |

| Simulator parameters used to evaluate device power management algorithms 1              | 32              |

| Parameters of different devices                                                         | 33              |

| Overview of simulator parameters used to evaluate global power management al-           |                 |

| gorithm                                                                                 | 52              |

| Tasks allocation through the MM algorithm                                               | 64              |

|                                                                                         | 76              |

|                                                                                         | 76              |

|                                                                                         |                 |

| <u>.</u>                                                                                | 84              |

|                                                                                         | 85              |

| Overview of simulator parameters used to evaluate demand bound function based           |                 |

| procrastination                                                                         | 00              |

|                                                                                         | 00              |

| Overview of simulator parameters used to evaluate alternative race-to-halt algorithms 2 |                 |

|                                                                                         | procrastination |

xviii LIST OF TABLES

# **List of Algorithms**

| 1  | Slack Management                                                                                                            | 46  |

|----|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | Enhanced Race-To-Halt Algorithm (ERTH)                                                                                      | 68  |

| 3  | Common Routines for ERTH, IRTH and LWRTH                                                                                    | 69  |

| 4  | Improved Race-To-Halt Algorithm (IRTH)                                                                                      | 74  |

| 5  | Light-Weight Race-To-Halt Algorithm (LWRTH)                                                                                 | 76  |

| 6  | Static Slack Container Algorithm (SSC)                                                                                      | 114 |

| 7  | Device Budget Reclamation Algorithm                                                                                         | 122 |

| 8  | Offline Algorithm for Multiple Sleep State Devices (SSC <sup>o</sup> )                                                      | 127 |

| 9  | Static Slack Container Algorithm for Multiple Sleep State Devices (SSC $^{m}$ )                                             | 129 |

| 10 | Aggressive Static Slack Container Algorithm for Multiple Sleep State Devices                                                |     |

|    | $(SSC^a) \dots \dots$ | 130 |

| 11 | Global Power Management Algorithm (GPM)                                                                                     | 149 |

| 12 | First Phase: Least Loss Energy Density (LLED)                                                                               | 162 |

| 13 | Alternative First Phase: Maximum Minimum (MM)                                                                               | 163 |

| 14 | Second Phase of Task Mapping (SP)                                                                                           | 165 |

| 15 | First Phase of Allocation                                                                                                   | 170 |

| 16 | Second Phase of Optimisation (SP)                                                                                           | 173 |

# **List of Acronyms**

ABS Anti-lock breaking system ACU Air-bag control unit

API Application programming interface

ASIC Application specific integrated circuit

BCET Best-case execution time

BE Best effort

BET Break-even-time

ccEDF Cycle-conservative earliest deadline first

CMOS Complementary metal-oxide-semiconductor

COLORS Composite low-power scheduling framework

Cons Consumption

CPU Central processing unit

DBF Demand bound function

DBFP Demand bound function based procrastination

DD Density difference

DFA Dynamic frequency allocation

DFA-LP Dynamic frequency allocation with reduced pessimism

DFR-RMS Device forbidden regions algorithm for rate monotonic schedulers

DIBL Drain-induced barrier lowering

DJP Dynamic job priority

DM Deadline monotonic

DM-PM Deadline monotonic with priority migration

Don Donation

DPM Dynamic power management

DTM Dynamic thermal management

DVFS Dynamic voltage and frequency scaling

DVS Dynamic voltage scaling

ED Energy density

EDF Earliest deadline first

EDS Energy-optimal device scheduler EEC Expected energy consumption EEDS Energy efficient device scheduling

ERTH Enhanced race-to-halt

ESSR Execution slack service register

FF First-fit

FIFO First-in-first-out FJP Fixed job priority

FPGA Field programmable gate array

xxii List of Acronyms

FRT Firm real time FTP Fixed task priority

GEDF Global earliest deadline first

GIDL Gate-induced drain leakage

Global-EDF Global earliest deadline first

GPM Global power management

GPS Global positioning system

HDMI High-definition multimedia interface

HPW High priority workload

HRT Hard real-time

HyWGA Hybrid worst-fit genetic algorithm

I/O Input/Output IC Integrated circuit

ILP Integer linear programming

IPW Intermediate priority workload

IRTH Improved race-to-halt ISR Interrupt service routine

ITRS International technology roadmap for semiconductors

LBET Low break-even-time

LC-DP Leakage control dynamic priority

LC-EDF Leakage control earliest deadline first

LCM Least common multiple

LEDES Low energy device scheduler

LLED Least Lost energy density

LLED-SP Least lost energy density and second phase

LLF Least laxity first

LLREF Largest local remaining execution first

LP Linear programming

LPW Low priority workload

LQS Low-power quasi-dynamic scheduling LRE-TL Local remaining execution TL-Plane

LWRTH Light-weight race-to-halt MDO Maximum device overlap MM Maximum minimum

MM-SP Maximum minimum with second phase

MOSFET Metal-oxide-semiconductor field-effect transistors

MT Matrix

MUSCLES Multi-state constrained low-energy scheduler

nMOS n-type metal-oxide-semiconductor field-effect transistors

NS Without sleep states

PARTPN Power-aware real-time petri-nets

PDMS\_HPTS Partitioned deadline monotonic scheduling with highest priority task split

PF Proportionate progress

PLL Phase lock loop

pMOS p-type metal-oxide-semiconductor field-effect transistors

PROC Procrastination algorithm based on Jejurikar et al. [JPG04] method

PUB Period upper bound RAM Random access memory List of Acronyms xxiii

RBED Rate-based earliest deadline first REC Reducible energy consumption

RM Rate monotonic ROM Read only memory

RT Real-time RTH Race-to-halt

RTOS Real-time operating system

SBET Small break-even-time

SBF Supply bound function

SFA Static frequency allocation

SMP Symmetric multicore platform

SMS Short message service

SP Second phase

SPARTS Simulator for power aware and real-time systems

SRA Slack reclamation algorithm

SRT Soft real-time

SSC Static slack container

SSSR Static slack service register

staticEDF Static earliest deadline first

TCDPM Thermally constrained dynamic power management

TE Total energy

TTL Transistor-transistor logic

USB Universal serial bus

WCET Worst-case execution time

WFD Worst-fit decreasing

# **List of Symbols**

| Hardware Platform                                 | Symbols                  |

|---------------------------------------------------|--------------------------|

| Hardware Platform                                 | $\pi$                    |

| No of processor types                             | M                        |

| Processor index                                   | m                        |

| Processor type <i>m</i>                           | $\pi^m$                  |

| Task-set allocated to a processor type <i>m</i>   | $	au^m$                  |

| Active power of a processor                       | $P_A^m$                  |

| Idle power of a processor                         | $P_{I}^{m}$ $ec{\S}^{m}$ |

| Vector of sleep states                            | $ec{\S^m}$               |

| Sleep index                                       | n                        |

| Number of sleep states                            | N                        |

| Sleep state of a processor                        | $\S^m_n$                 |

| Power of a sleep state                            | $P_n^m$                  |

| Transition delay of going into a sleep state      | $ts_n^m$                 |

| Transition delay of going out of a sleep state    | $tw_n^m$                 |

| Complete transition delay                         | $tsw_n^m$                |

| Transition delay                                  | $tr_n^m$                 |

| Power dissipated in transition phase              | $Ptr_n^m$                |

| Energy overhead of a sleep state                  | $Es_n^m$                 |

| Break-even-time of a sleep state                  | $bet_n^m$                |

| Average sleep energy                              | $\bar{E}^{\S^m_n}$       |

| Sleep threshold                                   | Ψ                        |

| Vector of frequencies                             | $ec{f}^m$                |

| Frequency index                                   | $\nu$                    |

| Number of frequencies                             | $V^m$                    |

| Frequency of a processor                          | $f_{v}^{m}$              |

| Power dissipation at a frequency                  | $P^m_{f^m_v}$            |

| Critical speed                                    | $f_{ m crit}^m$          |

| Dynamic power dissipation                         | $P_{dyn}$                |

| Leakage power dissipation                         | $P_{lkg}$                |

| Short circuit power dissipation                   | $P_{short}$              |

| Total power dissipation                           | $P_{total}$              |

| Energy                                            | E                        |

| Expected energy consumption                       | $EEC_{v}^{m}$            |

| Frequency Combination                             | $\Lambda_i$              |

| Set of frequency combinations                     | Λ                        |

| Energy consumption per unit time in the idle mode | $Sf_e$                   |

| Total Energy                                      | TE                       |

xxvi List of Symbols

| Speed up factor                                                                   | $\kappa'''$                                                                                                                            |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Helper variable                                                                   | ζ                                                                                                                                      |

| Average capacity of the heterogeneous platform                                    | $U^{avg}$                                                                                                                              |

| Effective utilisation of the hardware platform                                    | $U^{eff}$                                                                                                                              |

| •                                                                                 |                                                                                                                                        |

| System Model                                                                      | <b>Symbols</b>                                                                                                                         |

| Time                                                                              | t                                                                                                                                      |

| Task-set                                                                          | au                                                                                                                                     |

| Task-set size                                                                     | $\ell$                                                                                                                                 |

| Total utilisation                                                                 | U                                                                                                                                      |

| Task index                                                                        | i                                                                                                                                      |

| Task                                                                              | $	au_i$                                                                                                                                |

| Worst-case execution time                                                         | $C_i$                                                                                                                                  |

| Average-case execution time                                                       | $ar{C_i}$                                                                                                                              |

| Relative deadline                                                                 | $D_i$                                                                                                                                  |

| Minimum inter-arrival time                                                        | $T_i$                                                                                                                                  |

| Average minimum inter-arrival time                                                | $ar{T_i}$                                                                                                                              |

| Actual allocated budget                                                           | $A_i$                                                                                                                                  |

| Individual Task utilisation                                                       | $U_i$                                                                                                                                  |

| Job index                                                                         | k                                                                                                                                      |

| Job                                                                               | $j_{i,k}$                                                                                                                              |

| Absolute deadline                                                                 | $d_{i,k}$                                                                                                                              |

| Release time                                                                      | $r_{i,k}$                                                                                                                              |

| Current budget                                                                    | $a_{i,k}$                                                                                                                              |

| Actual execution time                                                             | $c_{i,k}$                                                                                                                              |

| Hyper-period                                                                      | H                                                                                                                                      |

| Task-set distribution                                                             | ξ                                                                                                                                      |

| Sporadic delay limit                                                              | Γ                                                                                                                                      |

| Best-case execution time limit                                                    | $C^b$                                                                                                                                  |

| Sporadic delay limit of a task                                                    |                                                                                                                                        |

| Best-case execution time limit of a task                                          | $C_i^b$                                                                                                                                |

| Vector of execution profiles of $\tau_i$ on different core types                  | $\Gamma_i \ C_i^b \ \stackrel{\Rightarrow}{\scriptscriptstyle{\sim}} \ C_i \ \stackrel{\rightarrow}{\scriptscriptstyle{\sim}} \ C_i^m$ |

| Vector of WCET of a task on a specific core type at different frequencies         | $\overset{ ightarrow}{C^m}$                                                                                                            |

| WCET at specific frequency                                                        | $C_i^m$                                                                                                                                |

| WCET at maximum frequency                                                         | $C_{i,v}^m$                                                                                                                            |

| Average execution time at maximum frequency                                       | $ar{C}_{\cdot}^{m}$                                                                                                                    |

|                                                                                   | $C^m_{i,v}$ $C^m_i$ $ar{C}^m_i$ $ar{E}_i$ $ar{E}_i^m$                                                                                  |

| Vector of average energy consumption profiles of $\tau_i$ on different core types | $E_i$ $ar{\mathcal{E}}^m$                                                                                                              |

| Vector of average energy consumption of a task on a specific core type at dif-    | $E_i^m$                                                                                                                                |

| ferent frequencies                                                                | Ēm                                                                                                                                     |

| Average energy consumption at specific frequency                                  | $E_{i,v}^m$                                                                                                                            |

| Average energy consumption at maximum frequency                                   | $ar{E}_i^m$                                                                                                                            |

| Utilisation of a core type m                                                      | $U^m$                                                                                                                                  |

| Utilisation of a core type <i>m</i> at frequency <i>v</i>                         | $U^{m,v}$                                                                                                                              |