FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Acceleration of Applications with FPGA-based Computing Machines: New DSL

**Daniel Alexandre Pimenta Lopes Fernandes**

Mestrado Integrado em Engenharia Informática e Computação

Supervisor: João Manuel Paiva Cardoso, PhD

July 25, 2019

### Acceleration of Applications with FPGA-based Computing Machines: New DSL

**Daniel Alexandre Pimenta Lopes Fernandes**

Mestrado Integrado em Engenharia Informática e Computação

Approved in oral examination by the committee:

Chair: João Paulo de Castro Canas Ferreira, PhD External Examiner: Ricardo Jorge Ferreira Nobre, PhD Supervisor: João Manuel Paiva Cardoso, PhD

July 25, 2019

## Abstract

Data analytics is often tackled by machine learning techniques. The algorithms involved frequently need to deal with large datasets, leading to long execution times. This kind of applications usually operates in domains where performance is critical. Developers have thus begun exploring hardware accelerators, such as graphics processing units (GPUs) and field-programmable gate arrays (FPGAs), to improve performance.

FPGAs provide a promising solution for hardware acceleration, configuration after manufacturing and reprogrammability. They are suitable targets for data analytics domains, providing higher performance and energy efficiency, which is becoming increasingly important in many systems nowadays. However, programming FPGAs is a complex task, usually accomplished using hardware description languages (HDLs), which require hardware design expertise. Several tools have been developed to raise the abstraction level of FPGA programming such as Xilinx's Vivado HLS. However, developers still need to be familiar with the tool they are using and the hardware they are targeting, in order to achieve efficient FPGA implementations. Therefore, if software developers are to adopt them, additional efforts must be made in standardizing the programming model, providing users with higher levels of abstraction.

One possible solution to this problem is the use of domain specific languages (DSLs), which have been proposed in many application domains. DSLs have also been developed to address the machine learning domain applied to Big Data. However, most of them do not target FPGAs. This dissertation proposes a new DSL for data analytics to target FPGA-based systems. The DSL compiler presented generates C code synthesizable by Vivado HLS for FPGA execution. The code is enhanced with optimization directives to take advantage of these devices. The DSL is evaluated using a human activity recognition (HAR) case study, taking into account performance, resource usage and productivity. The results show that data analytics applications can effectively be accelerated on FPGAs using a DSL approach. The main contributions of this work are towards the FPGA and data analytics communities (especially the ones using machine learning), as the developed DSL allows a new range of applications to be executed on FPGAs, thus achieving some of their benefits.

## Resumo

A análise de dados é muitas vezes abordada utilizando algoritmos de aprendizagem computacional. Estes algoritmos têm frequentemente de lidar com *datasets* muito grandes, o que leva a tempos de execução demorados. Este tipo de aplicações opera normalmente em dominios onde o desempenho é crítico. Os programadores começaram então a explorar aceleradores, como as *graphics processing units* (GPUs) e os *field-programmable gate arrays* (FPGAs), para melhorar o desempenho.

As FPGAs constituem uma solução promissora para a aceleração em *hardware*, configuração após fabrico e reprogramabilidade. Estes dispositivos são plataformas alvo adequadas para domínios de análise de dados, possibilitando níveis de desempenho e eficiência energética melhores, o que é cada vez mais um importante aspeto a considerar nos sistemas da atualidade. No entanto, programar FPGAs é uma tarefa complicada, normalmente concretizada utilizando linguagens de descrição de *hardware* (HDLs), que requerem conhecimentos de desenho de *hardware*. Diversas ferramentas foram desenvolvidas para melhorar o nivel de abstração da programação em FPGAs, como por exemplo o Vivado HLS da Xilinx. No entanto, os programadores ainda necessitam de estar familiarizados com a ferramenta e com a plataforma alvo, de modo a obterem implementações em FPGA eficientes. Desta forma, para estes dispositivos serem adotados por mais utilizadores, o modelo de programação terá de evoluir, a fim de aumentar o nivel de abstração.

Uma solução possível para este problema é o uso de linguagens de domínio específico (DSLs), que foram propostas em diversas áreas. Diversas DSLs foram também desenvolvidas para o domínio de aprendizagem computacional aplicada a *Big Data*. No entanto, a grande maioria não permite a execução em FPGAs. Esta dissertação propõe uma nova DSL para a área da análise de dados focando a execução em FPGAs. O compilador da DSL apresentado gera código C sinte-tizável pela ferramenta Vivado HLS. O código é enriquecido com diretivas de otimização, de modo a tirar partido da arquitetura destes dispositivos. A DSL é avaliada utilizando um caso de estudo de um sistema de reconhecimento de atividade humana (HAR), tendo em conta desempenho, utilização de recursos e produtividade. Os resultados demonstram que as aplicações de análise de dados podem ser efetivamente aceleradas em FPGAs utilizando uma DSL. As principais contribuições deste trabalho são direcionadas às areas das FPGAs e da análise de dados (especialmente aquelas que utilizam aprendizagem computacional), uma vez que a DSL desenvolvida permite que um novo leque de aplicações sejam executadas em FPGAs, tirando assim partido de algumas das suas vantagens.

## Acknowledgements

First and foremost, I would like to thank my supervisor João Manuel Paiva Cardoso for his support throughout this work. His knowledge in the field provided great contributions to the outcome of this dissertation.

I would also like to thank the folks over at the SPeCS lab, who have helped me throughout this dissertation, both clearing up any doubts I had and just generally giving me advice regarding the work.

Finally, I would like to thank my family for their support, not only throughout these few months, but also throughout my life in general. I am certain I wouldn't be where I am today without them.

**Daniel Fernandes**

"It would appear that we have reached the limits of what it is possible to achieve with computer technology, although one should be careful with such statements, as they tend to sound pretty silly in 5 years."

John von Neumann

## Contents

| 1 | Intr | oduction 1                                     |

|---|------|------------------------------------------------|

|   | 1.1  | Context                                        |

|   | 1.2  | Motivation                                     |

|   | 1.3  | Objectives                                     |

|   | 1.4  | Outline                                        |

| 2 | Bacl | kground                                        |

|   | 2.1  | Field-programmable Gate Arrays                 |

|   |      | 2.1.1 Architecture                             |

|   |      | 2.1.2 History                                  |

|   |      | 2.1.3 Programming FPGAs                        |

|   | 2.2  | Domain-specific languages                      |

|   | 2.3  | Summary                                        |

| 3 | Rela | ated Work 11                                   |

| - | 3.1  | DSLs targeting accelerators                    |

|   |      | $3.1.1 \text{ HIPA}^{CC}$                      |

|   |      | 3.1.2 Halide                                   |

|   |      | 3.1.3 PolyMage                                 |

|   |      | 3.1.4 OpenSPL                                  |

|   | 3.2  | DSLs and frameworks targeting machine learning |

|   |      | 3.2.1 OptiML                                   |

|   |      | 3.2.2 TensorFlow                               |

|   |      | 3.2.3 Theano                                   |

|   | 3.3  | Other DSLs and frameworks                      |

|   | 3.4  | Summary                                        |

| 4 | A ne | ew DSL for Data Analytics 27                   |

| - | 4.1  | DSL Engineering                                |

|   |      | 4.1.1 The Data Analytics Domain                |

|   |      | 4.1.2 Targeting FPGAs                          |

|   |      | 4.1.3 The DSL requirements                     |

|   | 4.2  | The new DSL                                    |

|   | 1.2  | 4.2.1 Declarations                             |

|   |      | 4.2.2 Input and Output                         |

|   |      | 4.2.3 Mathematical primitives and operators    |

|   |      | 4.2.4 Types                                    |

|   |      | 4.2.5 Machine learning primitives              |

|   |      |                                                |

#### CONTENTS

|    |             | 4.2.6    | Scope                 |        |   |     |     |   |     |     |     |   |     |   | <br>• |       | • |       |   | • | 38        |

|----|-------------|----------|-----------------------|--------|---|-----|-----|---|-----|-----|-----|---|-----|---|-------|-------|---|-------|---|---|-----------|

|    |             | 4.2.7    | Templates             |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 38        |

|    |             | 4.2.8    | Using header fil      | les.   |   |     |     |   |     |     |     |   |     |   | <br>• |       |   | <br>• |   |   | 39        |

|    | 4.3         | Compil   | ation Flow            |        |   |     |     |   |     |     |     |   |     |   | <br>• |       |   |       |   |   | 40        |

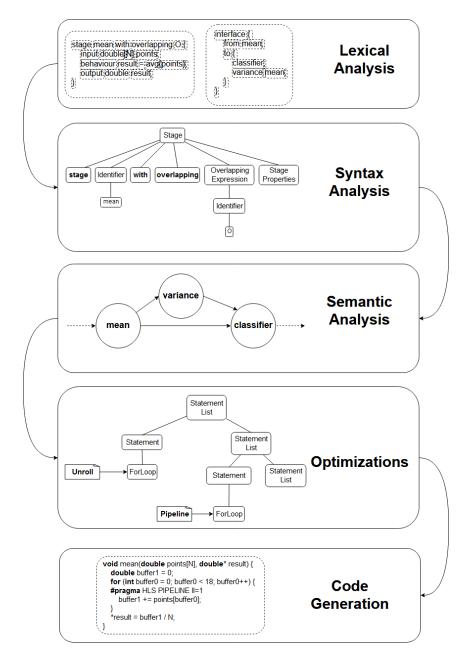

|    |             | 4.3.1    | Lexical Analysi       | s      |   |     |     |   |     |     |     |   |     |   | <br>• |       |   |       |   |   | 40        |

|    |             | 4.3.2    | Syntax Analysi        | s      |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 40        |

|    |             | 4.3.3    | Semantic Analy        | vsis . |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 40        |

|    |             | 4.3.4    | Code Optimizat        |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 43        |

|    |             | 4.3.5    | Code Generatio        | n      |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 44        |

|    | 4.4         | Targeti  | ng FPGAs              |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 45        |

|    |             | 4.4.1    | Using pragmas         |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 45        |

|    |             | 4.4.2    | Generating vali       | d code | e |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 46        |

|    |             | 4.4.3    | Optimizations .       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 47        |

|    | 4.5         | Implen   | nentation Details     |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 52        |

|    | 4.6         | Summa    | ury                   |        |   |     | ••• |   |     |     |     | • |     |   | <br>• |       | • | <br>• |   | • | 52        |

| 5  | Eval        | uation   |                       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 55        |

|    | 5.1         | Experin  | nental Setup          |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 55        |

|    | 5.2         | -        | tivity                |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 56        |

|    | 5.3         |          | nance                 |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 57        |

|    |             | 5.3.1    | Stage contributi      |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 57        |

|    |             | 5.3.2    | High-Level Syr        |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 58        |

|    | 5.4         | Hybrid   | Execution             |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 63        |

|    | 5.5         |          | ury                   |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 65        |

| 6  | Con         | clusions |                       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 67        |

| v  | 6.1         |          |                       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 67        |

|    | 6.2         |          | ch Questions          |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 67        |

|    | 6.3         |          | Work                  |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 69        |

| Re | feren       | ces      |                       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 71        |

|    | DCI         |          |                       |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 70        |

| Α  |             |          | mpiler details        |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | <b>79</b> |

|    | A.1         |          | nar                   |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 79        |

|    | A.2         | • •      | · · · · · · · · · · · |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 82        |

|    | A.3         | DSL C    | ompiler Usage .       |        | • | ••• | ••• | • | ••• | ••• | • • | • | ••• | • | <br>• | <br>• | • | <br>• | • | • | 82        |

| B  |             | -        | nental Results        |        |   |     |     |   |     |     |     |   |     |   |       |       |   |       |   |   | 85        |

|    | <b>B</b> .1 | High-L   | evel Synthesis .      |        |   |     |     |   |     |     |     |   |     |   | <br>• | <br>• | • | <br>• |   |   | 85        |

# **List of Figures**

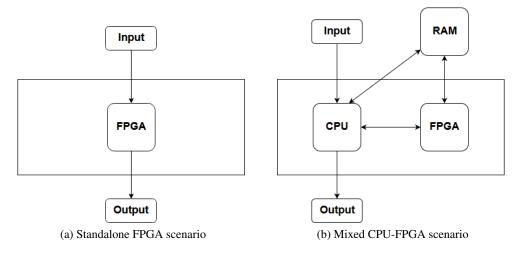

| 1.1 | Two different FPGA execution scenarios                                              | 3  |

|-----|-------------------------------------------------------------------------------------|----|

|     | (a) Standalone FPGA scenario                                                        | 3  |

|     | (b) Mixed CPU-FPGA scenario                                                         | 3  |

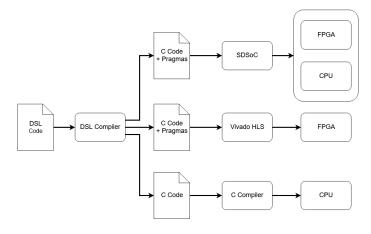

| 1.2 | DSL workflow                                                                        | 3  |

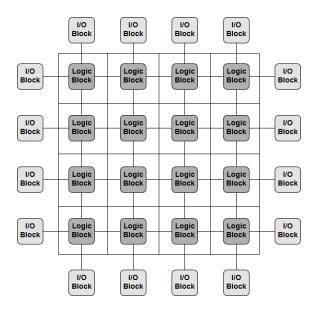

| 2.1 | FPGA architecture                                                                   | 6  |

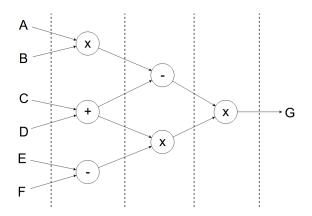

| 2.2 | Computation graph of $G = ((A \times B) - (C + D)) \times ((C + D) \times (E - F))$ | 7  |

| 3.1 | OpenSPL branch graph based on an example taken from The OpenSPL White               |    |

|     | Paper [53]                                                                          | 19 |

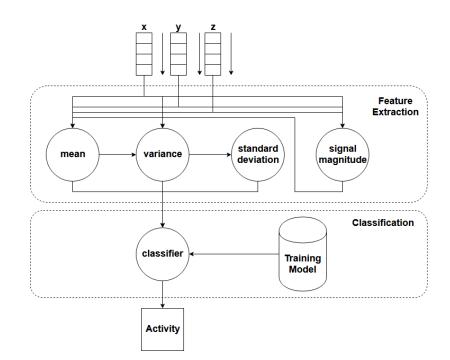

| 4.1 | Machine learning pipeline                                                           | 28 |

| 4.2 | DSL compilation flow                                                                | 41 |

| 4.3 | The block diagram resulting from the interfaces shown in Listing 4.17               | 43 |

#### LIST OF FIGURES

## **List of Tables**

| 3.1         | DSLs properties overview                                                                                                                                                   | 25       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.2         | DSLs evaluation overview                                                                                                                                                   | 26       |

| 4.1         | The main DSL and compiler requirements                                                                                                                                     | 29       |

| 4.2         | DSL mathematical primitives and operators                                                                                                                                  | 34       |

| 4.3         | DSL main types                                                                                                                                                             | 35       |

| 4.4         | DSL machine learning primitives                                                                                                                                            | 36       |

| 4.5         | Common directives used in Vivado HLS                                                                                                                                       | 47       |

| 4.6         | Compiler optimization strategy                                                                                                                                             | 49       |

| 5.1         | DSL and generated C code statistics for the HAR example (using floats). A simplified version of the HAR system (without the <i>signalMagnitude</i> stage) is also included | 56       |

| 5.2         | Contributions of each stage to the entire pipeline (using floats). These values are obtained executing the stages on the CPU using timers                                  | 57       |

| 5.3         | High level synthesis performance estimates for each stage with floats. Best speedups are shown in bold                                                                     | 58       |

| 5.4         | High level synthesis resource usage estimates for each stage with floats. Estimates exceeding the FPGA capacity are shown in bold                                          | 60       |

| 5.5         | High level synthesis performance estimates for each stage with doubles. Best speedups are shown in bold                                                                    | 61       |

| 5.6         | High level synthesis resource usage estimates for each stage with doubles. Esti-<br>mates exceeding the FPGA capacity are shown in bold                                    | 61       |

| 5.7<br>5.8  | Comparison between the best HLS versions and the CPU implementations, for<br>each stage. The best speedups are shown in bold                                               | 63       |

| 5.0         | (K) and communication (C) estimated clock cycles. Positive speedups are shown                                                                                              |          |

|             | in bold                                                                                                                                                                    | 64       |

| A.1<br>A.2  | DSL types                                                                                                                                                                  | 83<br>83 |

| <b>B</b> .1 | High level synthesis performance estimates for the mean, variance, standardDe-                                                                                             |          |

| В.2         | <i>viation</i> and <i>signalMagnitude</i> stages with floats                                                                                                               | 86       |

|             | with feature extraction grouped with floats                                                                                                                                | 87       |

| B.3         | Initiation intervals obtained for all the versions that used loop pipelining with floats                                                                                   | 87       |

| B.4         | High level synthesis resource usage estimates for all the stages with floats                                                                                               | 88       |

#### LIST OF TABLES

| B.5         | High level synthesis performance estimates for the mean, variance, standardDe-            |    |

|-------------|-------------------------------------------------------------------------------------------|----|

|             | viation and signalMagnitude stages with doubles                                           | 89 |

| B.6         | High level synthesis performance estimates for the <i>classifier</i> stage and the stage  |    |

|             | with feature extraction grouped with doubles                                              | 90 |

| B.7         | Initiation intervals obtained for all the versions that used loop pipelining with doubles | 90 |

| <b>B.</b> 8 | High level synthesis resource usage estimates for all the stages with doubles             | 91 |

## Abbreviations

| ASIC | Application-Specific Integrated Circuit |

|------|-----------------------------------------|

| ASSP | Application-Specific Standard Product   |

| AST  | Abstract Syntax Tree                    |

| BRAM | Block Random Access Memory              |

| CPU  | Central Processing Unit                 |

| DSL  | Domain-Specific Language                |

| DSP  | Digital Signal Processor                |

| FF   | Flip-Flop                               |

| FPGA | Field-Programmable Gate Array           |

| GPU  | Graphics Processing Unit                |

| HDL  | Hardware Description Language           |

| HLS  | High-Level Synthesis                    |

| IDE  | Integrated Development Environment      |

| IP   | Intellectual Property                   |

| IR   | Intermediate Representation             |

| LUT  | Lookup Table                            |

| ~ ~  | ~ ~ ~ .                                 |

SoC System on a Chip

### Chapter 1

## Introduction

This chapter introduces the dissertation. The context of the work is given first, followed by the motivation and objectives of the dissertation. The last section provides a general outline of this dissertation with a brief description of each chapter and its contents.

#### 1.1 Context

Ever since John Von Neumann wrote his famous first draft of what came to be known as the Von Neumann architecture [1, 2], computers have been, for the most part, developed following the principles therein. In modern times, however, some domains are moving computation towards hardware accelerators due to the constant need for better performance [3]. These devices attempt to employ a different paradigm of computation, favoring high degrees of parallelism. The most classic example is the computer graphics domain, which gave rise to the graphics processing units (GPUs) so familiar to everyone today. These devices, named after the graphics domain, were built to accelerate graphics processing. However, many more domains are embracing these architectures nowadays to improve performance [4]. Additionally, other architectures such as field-programmable gate arrays (FPGAs) are becoming more popular as well [5, 6, 7]. The parallel nature of these devices makes them appealing to several domains where performance is critical [8, 9]. Moreover, they also provide better energy efficiency than conventional central-processing units (CPUs) [10]. This is a characteristic that is becoming increasingly important in modern computing system, especially in embedded domains.

Data analytics [11] is the process of drawing conclusions based on thorough examination of data. The concept is often attached to machine learning, as the latter provides mechanisms for computers to analyze data, learn from it and thus be capable of making decisions based on the experience attained. Machine learning algorithms [12] must often deal with large amounts of data and the computations performed by them can become very complex. Problems arise when strict timing constraints must be met, especially in real-time environments. The volume of data and the inherent complexity of the algorithms significantly affect their performance. However, many algorithms display a heavy amount of parallelism. They are therefore appealing to accelerators,

#### Introduction

such as FPGAs, as these devices can take advantage of such parallelism to improve performance. Experiments have shown that targeting machine learning algorithms towards FPGAs can lead to critical performance gains [13].

#### **1.2** Motivation

FPGAs provide a potential solution to the problems inherent to data analytics. The performance associated with the machine learning algorithms used in this domain can be significantly improved with the use of these devices. However, FPGAs suffer from one key issue: programmability. FP-GAs are usually programmed using hardware description languages (HDLs) [14] such as VHDL or Verilog. These languages are hard to master for even expert software developers because they require hardware expertise. Software developers are used to programming in high level languages such as C or Java as these languages provide strong abstractions that allow them to efficiently develop programs without the need to know the underlying hardware being targeted.

In an attempt to solve this problem, several parties have tried to improve the programmability of FPGAs, introducing high-level synthesis toolsets such as Xilinx's Vivado HLS [15] or Altera's OpenCL Compiler for FPGAs [16]. However, even these environments are difficult to use as they require developers to be familiar with the tool they are using and the hardware they are targeting. Multiple domain-specific languages (DSLs) have been proposed to target FPGAs (see, e.g., [17]). One of the most popular domains is image processing, as this is an area that can also benefit greatly from the use of accelerators. The restriction to a single domain allows DSL compilers to more efficiently produce code that can be targeted for FPGA execution, because the compiler can leverage its knowledge of the domain to perform domain-specific optimizations.

Multiple DSLs and frameworks exist in the machine learning domain applied to Big Data [18, 19]. However, most of these do not target FPGAs and the same holds for many other DSLs and frameworks in other domains. Programming FPGAs requires much more effort than programming CPUs or even GPUs. Ultimately, the FPGA programming model needs to improve, in order for these devices to be adopted by the community [20]. For now, however, DSLs remain a viable and elegant solution to specific problems.

#### 1.3 Objectives

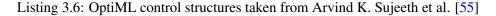

Targeting FPGAs can be done using two different approaches, illustrated in Figure 1.1. The first one uses the FPGA isolated. Inputs are sent in and out of the FPGA, so the entire program is hardware accelerated. The second approach involves a mixed CPU-FPGA solution. In this case, the CPU takes care of the main control flow of the program. The FPGA acts as a co-processor.

This dissertation proposes a new DSL for the data analytics domain targeting FPGA execution. The DSL provides machine learning oriented abstractions to allow users to naturally express their programs, hiding a number of implementation details. The main work includes the DSL compiler, responsible for generating optimized C code, synthesizable by the Vivado HLS toolset. This code

#### Introduction

Figure 1.1: Two different FPGA execution scenarios

can then be used to generate a bitstream for FPGA execution. Additionally, the DSL can also be used to program mixed CPU-FPGA systems, using Xilinx's SDSoC [21], as well as systems with a CPU only, using an ordinary C compiler. The DSL workflow is shown in Figure 1.2.

Figure 1.2: DSL workflow

The evaluation process of the developed DSL uses a human activity recognition (HAR) case study, taking into account both productivity and performance. For the performance evaluation, two scenarios are considered. The first one focuses on the FPGA code, in order to understand what sort of speedups can be obtained by targeting data analytics applications to a standalone FPGA. The second one considers a hybrid software/hardware solution, where the CPU manages the main control flow of the application, leaving the FPGA as a co-processor. The main goal of this work is to allow developers to create data analytics systems in a simplified manner and execute them on FPGAs, taking advantage of some of their benefits.

This dissertation's main contributions are targeted at the data analytics and FPGA communities. Data analytics users can benefit from a new DSL for the domain to target FPGA-based

#### Introduction

systems. Likewise, the introduction of a new DSL capable of targeting FPGAs improves the programmability of these devices, allowing a new range of applications to take advantage of them. As such, this dissertation aims to answer the following research questions:

- A.1 Can data analytics applications benefit from standalone FPGA execution using HLS?

- A.2 Can data analytics applications benefit from mixed CPU-FPGA execution using HLS?

- B.1 Can data analytics applications be targeted to FPGAs using a DSL approach?

- B.2 Can data analytics applications improve performance using a new DSL for FPGAs?

#### 1.4 Outline

This dissertation is organized as follows. Chapter 1 introduces the dissertation, providing context and motivation for the work proposed. Chapter 2 provides background into field-programmable gate arrays and domain-specific languages. Chapter 3 reviews related work in domain-specific languages and frameworks, with an emphasis on machine learning and FPGAs. Chapter 4 dives into the DSL developed as part of the main work of this dissertation. Chapter 5 evaluates the DSL and Chapter 6 concludes this dissertation.

### Chapter 2

## Background

This chapter provides some background knowledge related to field-programmable gate arrays (FP-GAs) and domain-specific languages (DSLs).

#### 2.1 Field-programmable Gate Arrays

Field-programmable gate arrays (FPGAs) are integrated circuits designed for configuration after manufacturing [10]. These circuits are composed as an array of logic blocks that can be configured by the user to perform combinational functions. The blocks can then be connected to each other with wires, thus allowing customers to create complex combinational circuits. FPGAs are usually programmed using hardware description languages (HDLs) such as Verilog or VHDL. Users can specify their circuits using these languages and use tools to synthesize bitstreams that can be fed to the FPGA fabric for reconfiguration.

FPGAs can provide hardware acceleration that increases performance over CPUs (see, e.g., [5, 13]). This happens because FPGAs emphasize parallelization and customization, allowing programs to be executed in a data-flow manner, as opposed to a control-oriented paradigm employed by traditional Von Neumann architectures [10].

#### 2.1.1 Architecture

As mentioned earlier, FPGAs contain an array of logic blocks. The blocks are interconnected to each other with wires and input/output blocks allow data to be sent to and from the FPGA. The FPGA can therefore be seen as a grid of logic blocks, where each block can operate concurrently. This provides huge benefits in terms of performance, because work can be distributed across the FPGA fabric. Moreover, the fact that logic blocks can be connected to other blocks allows computations to be deeply pipelined [22]. An overview of an FPGA architecture is shown in Figure 2.1.

FPGAs employ a data-flow computation paradigm, because all logic blocks can operate at the same time. Therefore, despite having lower clock speeds than CPUs, these devices can achieve even better performance in certain situations. They are, however, always limited by Amdahl's

Figure 2.1: FPGA architecture

Law [23], as the amount of parallel work always needs to be substantial for significant performance gains to be achieved. If the problem at hand is highly sequential, a CPU will outperform an FPGA, because the FPGA will not be able to take advantage of its architecture. For this reason, FPGAs are commonly used as coprocessors, allowing highly parallel computations to be performed in the FPGA fabric, leaving any sequential work to a CPU. The FPGA therefore takes a role similar to that of a GPU, as the latter is also used as a coprocessor to perform parallel work.

Another key aspect that makes FPGAs so appealing is the mapping of instructions to hardware. As mentioned earlier, conventional processing units adopt the Von Neumann architecture principles, because they follow a control flow paradigm, using memory to store and fetch instructions for sequential execution. FPGAs, on the other hand, have no fetching of instructions because the instructions are mapped into the circuit itself. Figure 2.2 shows the basic idea. Each node in the computation graph can be a logic block (more than one logic block would be necessary for larger operations, of course). Due to the flexibility of the FPGA, each block runs concurrently. Note that if a certain operation is being performed multiple times, this type of architecture can pipeline the execution, improving performance. In the case of Figure 2.2, all the nodes in the graph can execute at the same time as long as the FPGA keeps receiving input values. For example, the last node in the graph can be computing the multiplication of the values it receives in step (clock cycle) *i* while the nodes in the previous layer are executing the subtraction and multiplication for the values they receive in step i + 1. The last node would thus only need to wait 2 steps before receiving the first input values. After that, it would execute indefinitely.

This lack of instruction fetching and decoding allows FPGAs to achieve even better performance, because the circuit is tailored to a specific task. Of course, if a new algorithm is supposed to be executed on the FPGA, the fabric will need to be reconfigured. However, this is not a problem, because FPGAs were built to deal with specific tasks. If a system needs flexibility, a CPU is

Figure 2.2: Computation graph of  $G = ((A \times B) - (C + D)) \times ((C + D) \times (E - F))$

used instead. Some FPGA vendors provide dynamic reconfiguration features, but these add extra overhead and drive the FPGA into general purpose territory.

Each logic block usually contains a set of lookup tables (LUTs), flip-flops (FFs), digital signal processors (DSPs) and multiplexers. Lookup tables allow the user to store the functions desired while the flip-flops provide a mechanism for data to be persisted. The lookup tables can be configured with any logic function if the number of inputs in the LUT is enough. More complex functions might require the use of multiple LUTs or multiple logic blocks entirely. Current FP-GAs also include on-chip memories distributed along the fabric [10].

#### 2.1.2 History

FPGAs were developed in the 1980s to rival application-specific integrated circuits (ASICs). ASICs, unlike FPGAs, cannot be reconfigured. FPGAs presented an elegant solution over ASICs due to their reconfigurability. Although their performance was not quite as good as ASICs', their reconfigurability made them appealing to a wide range of markets. This rivalry still exists today, but both FPGAs and ASICs have evolved a lot since then [24]. Modern FPGAs have evolved into complex systems on a chip (SoCs) with several intellectual property (IP) cores attached to them [10]. IP cores can range from memory controllers to complete microprocessors. Nowadays, in fact, the reconfigurable part of the FPGA is usually less than half the entire fabric area. However, it is still the reconfigurable section that makes these devices so appealing. Application-specific standard products (ASSPs) have since showed up as well. These are like ASICs in that they provide specific features, but they tailor each solution to a wider audience.

#### 2.1.3 Programming FPGAs

FPGAs are usually programmed using hardware description languages (HDLs). However, because HDLs are difficult to master for even experienced software developers, researchers and FPGA vendors started providing ways of programming these devices in more familiar languages such as

C. This process became known as high level synthesis (HLS) [25]. This section dives into both HDLs and HLS.

#### 2.1.3.1 Hardware Description Languages

Hardware description languages are programming languages that describe hardware. Despite having syntax very close to that of traditional general purpose programming languages, they differ in several other aspects. Programs written using HDLs are essentially logic circuits, using logic gates to express them. A key aspect that drifts HDLs apart from traditional programming languages is the notion of time. The most most popular HDLs available are Verilog and VHDL [14], although several others exist.

#### 2.1.3.2 High Level Synthesis

While hardware description languages might be very convenient to map to hardware, they are difficult to program in. Most software developers are not used to programming at such a low level. Researchers and FPGA vendors thus started focusing on the concept of high level synthesis (HLS) [25]. High level synthesis allows software developers to program FPGAs using familiar high level languages such as C. The synthesis process usually generates HDL code, which can then be used by FPGA tools to generate the bitstreams to configure the FPGA.

High level synthesis differs from traditional compilation processes in several ways. Mapping a program to hardware is radically different than what compilers traditionally do. In essence, the most important steps of high level synthesis are schedulling, allocation and binding [26, 27]. These are defined as follows:

- Schedulling Assignment of operations to control steps;

- Allocation Selection of resources used to implement the intended operations;

- Binding Mapping of the operations to the hardware resources chosen during allocation.

All operations in a control step execute in the same clock cycle. It is thus important to maximize the number of operations executed in a control step to minimize the number of clock cycles on execution.

In addition to the three main synthesis tasks, optimizations are also somewhat different when synthesizing a hardware implementation. Even though certain optimizations, such as software pipelining or code transformations are also used in traditional compilers, high level synthesis allows additional hardware specific optimizations to be performed [25]. One common example is the use of custom bit-widths for variables in code. Traditionally, variables stick to strict variable types that have specific sizes. However, such sizes are not always adequate. For example, developers commonly use a 4 byte integer type for a loop counter, even when the loop runs very few times. When mapping to hardware, this conceives additional overhead. Therefore, high level synthesis can adjust the variables' sizes to be more efficient.

Several environments provide high level synthesis for FPGAs [28]. These range from commercial tools to academic projects. Most of them focus on synthesizing high-level languages such as C, C++ or Java.

Vivado High-Level Synthesis [15] is a high-level synthesis environment developed by Xilinx. It allows programs written in C, C++ and SystemC to be synthesized for FPGA execution. Vivado HLS comes with a full IDE as well as command line tools. This environment includes several wizards and scripts to help developers create their projects as well as synthesize their solutions. Vivado HLS also contains advanced features such as a debugger and an analysis perspective that allows synthesis results to be thoroughly examined. Code within Vivado HLS can be simulated, validated and synthesized as well as exported as an IP core. Moreover, the tool comes with a vast documentation with several examples and tutorials on each of the features described.

Vivado HLS C or C++ code is enhanced with optimization directives in the form of pragmas in the code. Directives can also be written to a separate file to provide developers with the opportunity to create multiple solutions in a project, each with its own directives. There are several directives available in Vivado HLS. Some of the most common compiler optimizations, such as loop pipelining and loop unrolling have their own directives. However, a number of Vivado HLS directives provide memory optimizations that are very specific to FPGAs.

While Vivado HLS allows the generation of IP cores, sometimes users want to develop mixed CPU-FPGA applications, using the FPGA as co-processor. Xilinx provides SDSoC [21] for these use cases. SDSoC allows applications to be executed on a mixed system consisting of a CPU and an FPGA. The application control flow is handled by the CPU, leaving parallel work to the FPGA. Note that this requires data transfers between CPU and FPGA every time an accelerated function is called. These transfers can be detrimental to the overall performance of the application. Therefore, SDSoC provides additional optimization directives targeted at communication. These allow the user to specify certain properties about the data transfers. For example, if an array is accessed in a sequential order, the accelerated function can begin executing as soon as it obtains the first element of the array. This access pattern can be configured using SDSoC optimization directives.

MaxCompiler [29] is a compiler developed by Maxeler Technologies that allows the generation of hardware implementations for execution on FPGAs. Developing an application requires users to create kernels, a manager wrapping those kernels and a host application [30]. The kernels and the manager are written in MaxJ, a Java-based high-level language that adds operator overloading [31]. The kernels represent the computations to be accelerated in hardware. The manager wraps the kernels and configures their interfaces to the host application. The host application is usually written in C or C++ and it launches the kernels using interface functions generated by the compiler. These functions are generated based on the kernel and manager code.

#### 2.2 Domain-specific languages

Domain-specific languages (DSLs) are languages focused on a given domain [32]. They differ from general purpose programming languages in that they cannot handle a wide range of problems. Instead, a DSL chooses to focus a given application domain, providing high level abstractions that are useful to developers targeting that domain. Therefore, programs written in a domain-specific language are usually very simple to develop and easy to read. The DSL attempts to hide anything that is irrelevant to the domain itself, allowing the user to focus on the domain only.

One of the key advantages of using a DSL over a general purpose language is the opportunity to obtain significant performance gains. Since DSLs are explicitly focusing on a particular domain, compilers can take advantage of such domain knowledge to generate more efficient target implementations. Compilers are used to applying several optimizations to code generated, even in general purpose languages. However, a DSL compiler can take certain domain-specific optimizations that cannot be taken in a general-purpose context. This allows DSLs to achieve better performance than general purpose languages.

In the context of FPGAs, DSLs are an elegant solution to the problems associated with programming these devices. As mentioned in Section 2.1.3, programming FPGAs is usually done using either hardware description languages (HDLs) or high-level synthesis (HLS) tools. HDLs are very difficult to use for even experienced software programmers. FPGA vendors developed HLS tools in an attempt to solve this problem. However, these tools are still rather difficult to use. Developers still require some knowledge regarding the hardware they are targeting. Moreover, some familiarity with the tool itself is also required, in order to achieve efficient implementations. DSLs provide an interesting solution to this problem and they have had extensive use in several application domains targeting FPGAs [17]. These languages raise the level of abstraction on FP-GAs because they rely on the compiler to deal with the FPGA specific issues, allowing the user to focus solely on the domain itself.

#### 2.3 Summary

This chapter provided an overview of the necessary background for this dissertation. The architecture, history and programmability of FPGAs was explained and the concept of DSLs was also touched upon, in order to understand their relevance, especially for the FPGA domain.

It is clear that a DSL is a valid approach to program FPGAs, especially for developers unfamiliar with these devices. The learning curve of both HDLs and HLS environments drives most software developers away from FPGAs, but DSLs can certainly be useful in fighting this issue, allowing these devices to be used by more people. The adoption of FPGAs can benefit several domains, as more applications can leverage the parallel nature of these devices to improve performance. This is especially relevant for real time systems where strict timing constraints must be met.

### Chapter 3

## **Related Work**

This chapter overviews related work in domain-specific languages (DSLs), focusing on accelerators (GPUs and FPGAs) and machine learning. Furthermore, some machine learning frameworks are also explored as these can provide interesting domain-specific abstractions as well.

#### 3.1 DSLs targeting accelerators

This section details some of the most relevant work done in DSLs targeting accelerators. Most of these DSLs target GPUs, but some approaches for FPGA execution are also described.

#### 3.1.1 HIPA<sup>CC</sup>

HIPA<sup>CC</sup> [33] is a framework that allows users to develop image processing algorithms, generating code targeting embedded GPUs. HIPA<sup>CC</sup> uses a C++-based embedded domain-specific language to specify image processing pipelines with useful abstractions. The HIPA<sup>CC</sup> compiler then generates the necessary code for different target languages (C++, CUDA or OpenCL). Furthermore, the framework has added support for Renderscript targets [34], allowing it to take advantage of heterogeneous hardware in embedded devices. The target language is chosen by the user and the resulting code can be executed on a GPU. This framework was originally built for medical image processing [35]. However, its features allow it to be used for any sort of image processing application.

The embedded DSL provides several interesting mechanisms that allow easier development of image processing pipelines. In addition, the DSL basically consists of C++ template classes provided by the HIPA<sup>CC</sup> framework. These classes are fully operational, meaning the code can be compiled using standard C++ compilers to run on a CPU. This can be used to compare results between GPU and CPU implementations.

The HIPA<sup>CC</sup> framework conceptualizes image processing algorithms in a dataflow manner. It views algorithms as a set of kernels that have inputs and outputs. The outputs are stored in a buffer, which in turn can be used as input to another kernel, forming complex pipelines.

Listing 3.1 shows a simple custom filter, using HIPA<sup>CC</sup>. Line 1 sets up the coefficients for this filter using a matrix. This matrix contains the constants that will be used to make the calculations inside the window. The image is loaded on line 10. Lines 12 and 13 set up boundary conditions. Boundary conditions are useful when a kernel tries to access out of bounds pixels. For example, if the operator uses a 5x5 window, it will access out of bounds pixels when it is in position (0,0). The boundary condition allows the values out of bounds to be mapped. In this case, the condition chosen was *BOUNDARY\_MIRROR*, which means the values will be mirrored. Finally, the iteration space for the output is created and the filter is built and executed. Executing the filter will call, for each window in the iteration space, the kernel function inside the filter definition, shown in Listing 3.2.

```

const int coefMatrix[5][5] = { { { 2, 1, 2, 1, 2 },

1

2

{ 2, 3, 2, 3, 2 },

3

\{7, 2, 6, 2, 7\},\

{ 2, 3, 2, 3, 2 },

4

5

{ 2, 1, 2, 1, 2 } };

6

7

Mask <int> mask(coefMatrix);

8

9

Image <uchar4> input(width, height);

input = image;

10

11

12 BoundaryCondition <uchar4> boundaryCondition(input, mask, BOUNDARY_MIRROR);

Accessor <uchar4> accessor(boundaryCondition);

13

14

Image <uchar4> output(width, height);

15

IterationSpace <uchar4> iterationSpace(output);

16

17

18

MyFilter myFilter(iterationSpace, accessor, mask);

19

20

myFilter.execute();

```

Listing 3.1: HIPA<sup>CC</sup> custom filter based on an example taken from Oliver Reiche et al. [36]

```

void kernel() {

1

2

int4 total = { 0, 0, 0, 0 };

for (int y = 2; y \ge -2; --y)

3

for (int x = 2; x \ge -2; --x)

4

total += mask(x, y) * convert_int4(inputAccessor(x, y));

5

total = max(total, 0);

6

total = min(total, 255);

7

output() = convert_uchar4(total);

8

9

}

```

Listing 3.2: HIPA<sup>CC</sup> Kernel based on an example taken from Oliver Reiche et al. [36]

The kernel function is where the computations happen. For this filter, the values in the window (5x5) are multiplied by their corresponding value in the coefficient matrix. The result is summed. The sum is then normalized to obtain the value for the pixel, which is assigned to the output function in line 8. Note that the traversal of the matrix is entirely hidden from the programmer. All he/she has to do is write the kernel, which is what really matters in the algorithm. The traversal is handled automatically using the framework classes.

Oliver Reiche et al. [36] extended the framework to allow the DSL code to be translated to a form capable of being executed on an FPGA. The extension is focused on generating code for Vivado HLS. It therefore takes the C++ embedded DSL code and generates C++ code that can serve as input to the Vivado HLS suite. Note that the C++ code generated has additional annotations (some of them in the form of pragmas) to allow Vivado HLS to generate better HDL code and thus better FPGA implementations.

The framework is based on the Clang/LLVM compiler infrastructure [37]. The Clang frontend is used to parse the DSL code and generate an Abstract Syntax Tree (AST). This intermediate representation (IR) is then used to generate two kinds of code: the host code and the kernels. The host code is the driver, managing the kernels, launching them and sending them data. The kernel code contains the specified computations to run on the accelerator using the target language chosen (CUDA, OpenCL, Renderscript). The generated AST from the Clang frontend is used to create the necessary adjustments to the target code, so it can be compiled by Vivado HLS.

The host code is generated by obtaining a structural representation of the intended image processing pipeline. This representation is built by traversing the AST looking for buffer allocations, memory transfers and kernel executions. These are identifiable because they use compiler known classes (part of the framework). The resulting representation is a graph that contains nodes for processes (kernel executions) and space (buffers). The graph is traversed backwards in depth first search (DFS) fashion. This way, irrelevant computations are rightfully pruned from the code. The process nodes are translated into kernel executions and the buffers are used to create Vivado HLS stream objects.

Several problems need to be dealt with to generate efficient C++ code. For example, the embedded DSL uses masks to make calculations. When convolutions are calculated using the mask constants, the resulting value range will need to be adjusted, depending on how the mask constants are represented. If the constants are represented as integers, the convolution will require the multiplications and a normalization step at the end. However, if floating point values are used (and all of them add up to 1), then the normalization step at the end is not needed. It turns out that on FPGAs, the former choice has the least impact on resource usage. HIPA<sup>CC</sup> does not support the use of floating-point values, so the values need to be converted to integers. Note that this conversion requires the additional normalization step at the end.

To generate the device code (kernels), an image processing C++ library is used. Masks are known at compile time (hence the use of constants). This is important to make the necessary transformations to the mask, as described earlier. In addition, the constants can be propagated throughout the code, further improving efficiency. Image dimensions need to be known at compile

time as well, to take additional advantage of Vivado HLS and to achieve more efficient FPGA implementations.

Finally, to take further advantage of the Vivado HLS suite, several optimizations are made. Synthesis directives in Vivado can be placed in the code via pragmas or in a separate file. The most common and obvious directives are placed in the code, while the others are put in a separate file to allow users to manipulate them to better tune their designs. Loop counter variables are automatically tuned by Vivado HLS, in order to avoid having to specify the exact necessary bitwidth. Note that changing the image dimensions would require changing the bit-width. This way, Vivado HLS does it without help from the user. Vivado HLS uses assertions to infer the required bit-widths. Vector types are also translated to C structures. Note that the motivation behind vector types is that they are usually present in GPU programming models and they are actually a useful way to represent data in image processing algorithms. However, to program FPGAs with Vivado HLS, this choice is not available, so the vector types are translated to structures that can be easily manipulated. Finally, some delays might occur in certain algorithms due to different window sizes in local operators on a pipeline. The solution here is to enforce a delay on the faster operators.

The HIPA<sup>CC</sup> implementation on an FPGA [36] was evaluated in comparison with implementations using the OpenCV library from Xilinx as well as expert implementations executing on GPUs. The benchmarks used were the Laplacian filter, Harris Corner and the Optical Flow image processing pipelines. The HIPA<sup>CC</sup> extension was executed on a Xilinx Zynq 7045 FPGA. Other implementations were executed on the Nvidia Tesla K20 GPU and the ARM Mali-T604 embedded GPU. The HIPA<sup>CC</sup> extension outperforms the Mali by factors of 3 for the Laplacian filter and 19 for the Harris Corner. It outperforms that same GPU for the Optical Flow pipeline by a factor of 456, but this pipeline took abnormally long on the Mali which makes its comparison less relevant. The Tesla outperforms the FPGA by factors of 2 for the Optical Flow and 30 for the Laplacian filter. Throughput shows equivalent values as this metric is highly influenced by performance. Energy efficiency for the FPGA Laplace version is the highest of all the algorithms and it is 19 and 34 times higher than the equivalent Tesla and Mali versions, respectively. Resource usage is better for the HIPA<sup>CC</sup> extension than the OpenCV equivalents, with 24 times less used LUTs.

Özkan et al. [38] extended the framework even further with the addition of Altera FPGAs through Altera's OpenCL. The approach is somewhat similar to the one used for Vivado HLS, generating a streaming pipeline for execution on the FPGA. Some of the optimizations used are similar to the ones present in the previous extension, although the details of their implementation differ. For example, the bit-width issue mentioned earlier was solved by Vivado HLS itself through the use of arbitrary bit-widths. Although Altera's OpenCL provides a similar mechanism, the OpenCL standard does not. To avoid the loss of portability, this extension uses a bit-wise *AND* to handle the bit-width issue.

Overall, HIPA<sup>CC</sup> is one of the most complete image processing frameworks out there, as it now provides support for CPUs (using C++), GPUs (using CUDA or OpenCL), Android (using Renderscript), Altera's FPGAs (using Altera's OpenCL) and Xilinx's FPGAs (using Vivado HLS) [39].

#### 3.1.2 Halide

Halide [40] is a DSL that can be used to develop image processing pipelines. The Halide compiler can generate code for both CPU execution, as well as for CPU + GPU runs. The language provides several abstractions to aid in the development of image processing algorithms.

Image processing pipelines usually have several stages. Each stage operates on a given input. The input can be an entire image or parts of it. The first stage gets the original image and sends the results of its computation to the next stages and so on until the output is obtained on the last stage. The operations performed by the stages can vary a lot. Some stages might perform stencil computations while others might do resampling or even simple point-wise operations. The key aspect here is that there is a lot of diversity in the type of operations that might be performed. For this reason, choosing the best way to setup the algorithm to obtain the best performance is not a trivial task. This task can be referred to as finding the algorithm's schedule. The schedule specifies the way in which operations are performed and what the storage constraints should be. There are multiple strategies to enhance an algorithm's performance. However, strategies are not always compatible. Many image processing applications try to achieve good performance by making the computations in a parallel fashion. Others might try to achieve better data reuse, because many stages in a pipeline might operate on a window and can thus benefit from reducing redundant computations. These techniques are usually incompatible, because to achieve data reuse, an ordering needs to be enforced, thus sacrificing parallelization. Moreover, the schedule for one of the stages should not be applied to all the other stages, because the proper schedule is stage dependent. That is, a good schedule for one stage might be terrible for another. Additionally, the schedule for a given stage is also dependent on the stages it uses values from. This is an important aspect, because finding the right schedule for the algorithm is not about finding the best schedule for each stage. Ultimately, the key is finding the combination of stage schedules that achieves the best overall algorithm performance. If one considers that some image processing applications have hundreds of stages with a huge amount of different operations, then one can easily understand that scheduling is a very demanding task.

Halide attempts to act on this problem by raising the level of abstraction. Its focus is to decouple algorithms from schedules [41, 42]. The algorithms are the textual representation of the image processing pipelines. This description makes no assumptions about the order in which operations will be performed, nor does it care about storage concerns. The schedule specifies all these characteristics. The DSL uses a function construct to represent a stage in the pipeline. These functions can use other functions so, for the most part, all the stages in the pipeline can be represented in almost the same number of lines. Halide also provides reduction operations. These are represented with an initial value function and a recursive reduction function. They also need a reduction domain, which specifies the order in which the reduction is performed. Reductions can be helpful in operations like histogram equalization, for example.

Listing 3.3 shows a simple example of the Halide syntax. It shows a pipeline with 3 stages. The first one blurs the image over x and the second does the same over y. The last stage is the

output function and it multiplies the result from the previous stage by a constant. The syntax is fairly straightforward. Note that this specification entails only the computations to be done. It does not say anything regarding the schedule.

```

1 Func stage1(x, y) = input(x - 2, y) + input(x - 1, y) + input(x, y) + input(x + 1,

y) + input(x + 2, y)

2 Func stage2(x, y) = stage1(x, y - 2) + stage1(x, y - 1) + stage1(x, y) + stage1(x,

y + 1) + stage1(x, y + 2)

3 Func output(x, y) = stage2(x, y)*10

```

Listing 3.3: Halide example filter based on an example taken from Jonathan Ragan-Kelley et al. [43]

The schedules in the Halide language are defined by telling the compiler when and where each function is computed and where its results are stored. The function traversal can be sequential or parallel. Dimensions with constant size can be unrolled or vectorized as well as reordered, choosing either row or column-major ordering. Dimensions can additionally be split by a factor, thus allowing the grid representing the image being processed to be decomposed as a set of tiles. In the example above, for example, the *output* function dimensions can be split by a factor, effectively tiling that dimension. The same can be done for *x* and this variable can even be vectorized.

The compilation works by first taking the Halide textual representation of the image processing pipeline and creating a set of loops to execute the algorithm. In this stage, the bounds of the loops and the sizes of the storage buffers are represented by symbolic constants. The second phase is bounds inference. It is here that the bounds for the loops and the buffer sizes are inferred. The third stage looks for sliding window optimizations and storage folding. The focus here is to find better data reuse by looking at which functions use values computed by previous iterations. This avoids redundant computation by sacrificing a bit of parallelism. Storage folding allows the buffers to be shrinked, because many functions compute local operations. That is, many functions use only a subset of the entire buffer (because they might only use the past few scanlines). For this reason, if a function only needs the last 3 scanlines from a buffer, then the buffer can be of size 3, thus reducing the peak memory use and working set size. The fourth stage flattens multi-dimensional loads, stores and allocations into a single dimensional equivalent. Thus, the image is treated as if it were a single line. The fifth stage performs loop unrolling and vectorization according to the schedule. Finally, the Halide IR representation at this point is ran through standard constant folding and dead code elimination passes before being lowered to LLVM IR. Additionally, functions can also be scheduled to run on a GPU. This means that the functions are implemented as kernels that execute on the GPU. If GPU code generation is specified in the schedule, the resulting code is a hybrid implementation (CPU + GPU) of the image processing pipeline.

Previous versions of the Halide DSL required users to specify the schedules by hand. The authors have since developed their own autotuner to aid in this process [43, 44, 45]. The auto tuner applies stochastic search to the schedule search space to find a good schedule. Genetic

algorithms are used for the search, with an initial population of 128 schedules. Some of the starting schedules are selected by a weighted coin which chooses, for each function, one of two schedules: a fully parallelized and tiled version or a parallelized over *y* version. Other starting schedules are created applying breadth first schedules to functions (that is, compute and store at the root outermost granularity). The algorithm then iteratively finds new schedules using elitism, crossover, mutations and random individual generation.

The results were measured by developing Halide versions of several algorithms and comparing them to expert implementations in other languages (namely C++). The Xeon W3520 x86 CPU and the NVIDIA Tesla C2070 GPU were used to execute the implementations. The metrics used were speedup and lines of code. GPU versions were also generated for some of the algorithms to see how they perform. The benchmarks used were a blur filter, a camera pipeline, multi-scale interpolation, bilateral grid and local Laplacian filters. The results show that the Halide algorithms get better performance in all the benchmarks while at the same time providing the user with a better experience, because each one requires fewer lines of code. The bilateral grid is by far the most successful in terms of productivity with only 36 lines of code as opposed to the 158 of an expert implementation. The speedup is 4.4 over the expert implementation, for this example, which is the highest of all the speedups. However, all Halide versions have performance gains over the expert implementations. Only one comparison was made to a GPU version, with a speedup of 2.3 for the bilateral grid as well. Local Laplacian filters implemented in Halide for GPU execution have a speedup of 9 over a CPU implementation of the same pipeline (no GPU expert implementation was available). The auto tuner for the examples took between 2 hours to 2 days to find a schedule for each algorithm, which makes it impractical in some real-world applications. However, the performance benefit from using Halide is clear as it generates very fast implementations, which can be useful in some cases (for example, if the input image is of fixed size over time).

Jing Pu et al. [46] developed an extension to Halide to target FPGAs. Their approach uses C target code for Vivado HLS. Their compiler generates a hybrid implementation of the algorithms, with some parts targeting the FPGA and others targeting the CPU. They take advantage of several parts of the original Halide compiler, using the Halide IR to generate a data-flow graph. This graph can then be used to generate hardware implementations of the kernels. For the software section, they rely mostly on the Halide ARM backend, with additional passes to introduce the hardware calls in the correct places. The extension was evaluated in comparison with HIPA<sup>CC</sup> [36] and an HLS video library. Their results show that their extension to Halide can obtain equivalent results to the other two, saving 6% in BRAM when compared to the HIPA<sup>CC</sup> for the Harris Corner benchmark. When compared to GPUs, their extension exhibits 1.9x more throughput and 6.1x higher energy efficiency. The results are even better on both metrics when evaluated against the CPU implementations.

#### 3.1.3 PolyMage

PolyMage [47] is a DSL used for image processing applications. It is an embedded DSL as it uses Python as host language. The compiler generates C++ code using OpenMP to employ a

shared memory model for execution on CPUs. Code is written in the form of image processing stages. Each stage is defined as a function. Function declarations provide the inputs and the definitions give a description of the computation to be made. PolyMage provides several high level image processing related constructs that allow the user to write very complex image processing applications with few lines of code [48].

An example of a kernel specification using the DSL is given in Listing 3.4. Note how the definition of the pipeline is very simple as it uses predefined language constructs like Stencil. Since image processing pipelines have several common operations well defined, these are all given their very own constructs, which reduces development effort. For example, many image processing pipelines use matrices to compute values. These matrices are passed to the Stencil construct in this example, which in turn makes the actual calculations using the parameters it received, hiding implementation details from the user.

```

Listing 3.4: PolyMage kernel based on an example taken from Nitin Chugh et al. [49]

```

Nitin Chugh et al. [49] provide an extension to the PolyMage compiler to allow execution on FPGAs. The extension generates C++ code with Vivado HLS directives. It is therefore targeted at the Vivado Design Suite and Xilinx FPGAs. Results show that this extension allows FPGA implementations to reach speedups ranging from 1.05x to 15.60x when compared to CPU optimized implementations. PolyMage FPGA implementations also achieve better performance (1.45x to 1.59x) than Xilinx's predefined OpenCV implementations of two of the algorithms used as benchmarks (Harris Corner Detection and Unsharp Mask).

More recent work by Abhinav Jangda et al. [50, 51] provides an algorithm to improve loop fusion. The case study used to apply the algorithm is PolyMage, although their focus is the image processing domain in general. Therefore, their proposal could be adapted to other DSLs, such as Halide [40]. Their results show improvements against both the original PolyMage and Halide's approaches towards loop fusion.

## 3.1.4 OpenSPL

OpenSPL [52] is a domain-specific language targeting the spatial computing domain. Its focus is providing developers with strong abstractions that allow them to create complex hardware accelerated programs from software defined descriptions, bridging the gap between software and hardware.

The DSL contains a model of Spatial Computing Substrates (SCS), from which different hardware technology can be targeted, from Dataflow Engines from Maxeler to Automata Processor

Engines from Micron or even future Quantum Processing Units [53, 54]. They can thus target FPGAs to allow users to take advantage of their parallel features.

The language extends MaxJ [30], providing additional hardware abstractions more useful to software developers. Computations are done inside kernels. Inputs and outputs are managed using functions, a paradigm already familiar to high level language programmers. A small example of a kernel in OpenSPL is shown in Listing 3.5.

```

1 class MyKernel extends Kernel {

2  MyKernel() {

3   SCSVar input = io.input("input", scsFix(12));

4   SCSVar output = (input < 25) ? input + 2 : input - 2;

5   io.output("output", output, scsFix(13));

6   }

7 }</pre>

```

Listing 3.5: OpenSPL kernel based on an example taken from The OpenSPL White Paper [53]

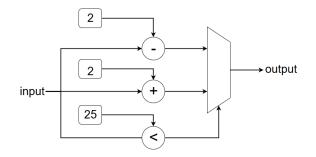

This example shows how branching can be parallelized by mapping the branch to a set of operations that execute in parallel, with their results being inputs to a multiplexer. The branch condition can then be set as the multiplexer selection input to choose the appropriate result, that is, the right branch based on the condition, as shown in Figure 3.1.

Figure 3.1: OpenSPL branch graph based on an example taken from The OpenSPL White Paper [53]

This shows how the control flow of the kernel shown in Listing 3.5 is mapped into a data flow in Figure 3.1. Moreover, bit widths can be set for each variable used, allowing stronger flexibility.

The OpenSPL compiler generates MaxJ code which can be fed to the MaxCompiler to produce a VHDL description of the application [54]. The bitstream can then be generated for execution on the FPGA.

These are just some of the features available in OpenSPL. The language, while not as high level as general-purpose programming languages like Java or C, still presents a big upgrade from average HDLs such as Verilog or VHDL, which is a benefit for software developers wishing to port their programs to hardware accelerators.

# **3.2** DSLs and frameworks targeting machine learning

This section surveys some related work on DSLs and frameworks targeting machine learning. None of the projects described here has any official support for FPGA execution. Nonetheless, some solutions have been proposed to solve that problem and these are therefore also described throughout each subsection.

# **3.2.1 OptiML**

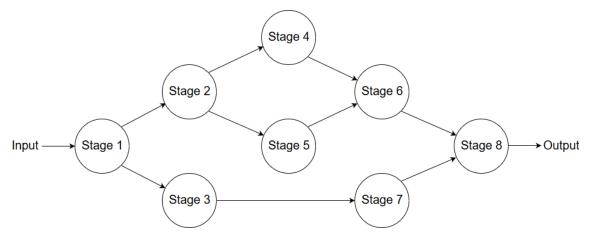

OptiML [55, 56] is a domain-specific language targeting the machine learning domain. It is embedded in Scala and it can be executed on CPUs and Nvidia GPUs. The language uses several machine learning abstractions, such as *Image*, *TrainingSet*, among others. Although these are mapped to either matrices or vectors in the background, they convey certain domain-specific properties that allow the compiler to generate more efficient code. Some of the control structures built into the language are shown in Listing 3.6.

```

1 // sums

2 val result = sum(lowerBound, upperBound){ i =>

3   <ith value to sum>

4 }

5

6 // creates a new vector

7 val newVector = (0::end) { i =>

8   <ith value of the new vector>

9 }

```

These abstractions allow the users to specify their machine learning algorithms in a clear and compact way. Listing 3.7 shows one of the steps in the k-means clustering algorithm.

```

1 // centroids is a matrix containing the centroids. Each row is a centroid (vector)

2 // x is a matrix containing the samples. Each row is a sample (vector)

3 val closestCentroids = (0::m) {i =>

4 val distances = centroids mapRows { centroid =>

5 // distance from the current sample to the current centroid

6 ((x(i)-centroid)*(x(i)-centroid)).sum

7 }

8 distances.minIndex

9 }

```

Listing 3.7: OptiML k-means centroid calculation taken from Sujeeth et al. [55]

This excerpt calculates the distance between each sample and each centroid and builds a vector containing, for each element, the closest centroid. Vector *closestCentroids* thus contains, for each entry *i*, the index into the centroid matrix that is the closest to sample *i*.

OptiML code is compiled using the Delite Compiler Framework and Runtime [57, 58, 59]. Delite allows the creation of implicitly parallel domain-specific languages that can be targeted to heterogeneous platforms using the Delite runtime. Although Delite users need to make their DSLs embedded in Scala, they can take advantage of certain features built into the framework. One of the key aspects that DSLs take advantage of is the potential for domain-specific optimizations to be performed, leveraging the knowledge the compiler has about the domain. Delite provides users with a modular approach to implementing DSLs that allows users to create domain-specific optimizations for their DSLs by extending certain classes existent in the framework [60]. Moreover, since the framework comes with a variety of predefined compiler optimizations, DSL developers can choose which ones to reuse and which ones to extend.

OptiML code fed to the Delite compiler is used to generate an execution graph: the Delite Execution Graph (DEG). The compiler generates target code for each kernel in the DEG. Delite attempts to generate code in Scala, C++ and CUDA, when possible. The runtime then chooses which version to use during execution. This improves flexibility as it allows the runtime to schedule the kernels in the DEG taking into account dynamic information such as resource availability and input size [61].

While OptiML targets only CPUs and GPUs, George et al. [62] provide an approach to develop FPGA implementations. Their extension targets Xilinx FPGAs using Vivado HLS. In addition to the traditional generic optimizations provided by languages developed in Delite, this extension adds loop unrolling, loop pipelining, as well as the introduction of local buffers and loop sectioning, leveraging domain-specific knowledge.

The extension proposed by George et al. [62] has been evaluated using machine learning benchmarks, such as Nearest Neighbor, Outlier Counter, 1-D Correlation and 1-D Normalization. Versions were implemented in both OptiML and C++ using OpenMP. The former were executed on FPGAs while the latter were executed on CPUs. The CPU versions outperform the FPGA versions in performance, although the gap is more evident in the multi-threaded implementations. In terms of energy efficiency, the single-threaded CPU versions spend between 1.8x and 4.4x more energy in fixed point dominated applications than the OptiML FPGA implementations. The multi-threaded CPU versions spend between 1.3x and 3.5x more energy than the OptiML versions executing on FPGAs, on all fixed-point dominated applications.

#### 3.2.2 TensorFlow

TensorFlow [63] is an open-source framework for machine learning. It was developed by Google and it is largely based on their experience with the DistBelief system [64]. The framework focuses mostly on neural networks and deep learning models [65], expressing such computations as data-flow graphs. These graphs hold both the computations and the state on which these computations operate on. The models usually perform computations on multi-dimensional arrays called tensors.