FACULDADE DE ENGENHARIA DA UNIVERSIDADE DO PORTO

# Isolated and Bidirectional DC-DC Converter for Electric Vehicles

Pedro Afonso Rodrigues

Integrated Masters in Electrical and Computer Engineering

Supervisor: António Pina Martins Co-Supervisor: Diogo Varajão

July 24, 2018

## Abstract

Nowadays, the demand for electric vehicles has grown at a rapid pace, and to meet this need and due to the environmental constraints, the power electronics fields has continuously looked for innovative solutions to make conversion systems lighter and compact. DC-DC bidirectional converter topology is an excellent example of an interface between two DC bus and is typically found in electrical vehicle storage systems.

With the premises mentioned early, a DC-DC converter is required for this dissertation project to controls the power transfer in both directions with the best efficiency and the lowest volume. In this way, emerging semiconductor technologies will be analyzed as well as the feasibility of bringing these components into the conversion system. In the first part, a converter topology in the power electronics field is presented with the purpose of studying, selecting and implementing a DC-DC converter with high power density for application in electric vehicles. State of the art presents the research and comparison between different DC-DC converter topologies and with focus on the isolated dual-active-bridge (DAB) and respective modulation techniques that allow to enhance efficiency and make the converter more compact and lighter, highlighting the inherent advantages and limitations of each one.

The DAB topology is analytically studied and modeled by a detailed model that includes the major power losses. Closed-loop control is design for the DAB converter supported by a detailed model transfer function. Market research of semiconductors using silicon carbide technology is shown. The efficiency of the DAB converter at different switching frequencies, from 40 kHz to 80 kHz is presented. A gate driver circuit was designed to drive a half bridge structure, and the board circuit schematic is presented.

*Keywords* – Dual-active-bridge, bidirectional and isolated DC-DC converter, high-frequency transformer, thermal model for semiconductor, Silicon Carbide MOSFET.

## Resumo

Atualmente, a procura por veículos elétricos tem crescido a um ritmo acelerado, e de forma a responder a essa necessidade e devido às restrições ambientais, a área da eletrónica de potência tem procurado continuamente soluções inovadoras para tornar os sistemas de conversão mais leves e compactos. Os conversores bidirecionais DC-DC são um bom exemplo de topologia que serve de interface bidirecional entre dois barramentos, e é tipicamente encontrada em sistemas de armazenamento de veículos elétricos.

Com as premissas mencionadas atrás, para o trabalho desta dissertação é requerido um conversor DC-DC que controle a transferência de energia nos dois sentidos com a melhor eficiência e no menor volume. Desta forma, semicondutores com tecnologia emergente serão analisados, assim como a viabilidade de trazer estes componentes para o sistema de conversão. O documento apresenta numa primeira parte o estudo de topologias de conversores DC-DC existentes na área da eletrónica de potência com o objetivo de estudar, selecionar e implementar um conversor DC-DC com elevada densidade de potência para aplicação em veículos elétricos. O estado da arte apresenta a pesquisa e comparação entre topologias de conversores bidirecionais DC-DC dando especial atenção foco ao conversor isolado de dupla ponte (DAB) com componentes ativos e as respetivas técnicas de modulação, onde são analisadas com vista a melhorar a eficiência de conversão, realçando as vantagens e limitações inerentes das mesmas.

A topologia DAB é estudada analiticamente e modelada através de um modelo detalhado que inclui as perdas de potência gerais. Um controlo em malha fechada é desenvolvido para o conversor DAB com o auxílio da função de transferência do modelo detalhado. O estudo de mercado de semicondutores com a tecnologia carboneto de silício é apresentado. A eficiência do conversor DAB obtida para diferentes frequências de comutação, de 40 kHz a 80 kHz é apresentada. Um circuito de driver foi projetado para comandar uma estrutura de meia ponte, e o esquema do circuito é apresentado.

## Agradecimentos

Começando por agradecer ao professor António Martins por ter mostrado disponibilidade e paciência em acompanhar o meu trabalho desenvolvido ao longo desta dissertação.

Agradecer também à equipa da AddVolt me ter acolhido e me fazer sentir em casa. Foi um prazer ter feito parte de uma equipa jovem e com ambições inovadoras. Desejo o maior sucesso para toda a equipa. E, como não podia deixar de ser, um agradecimento especial ao Eng. Diogo Varajão pelo apoio e disponibilidade para me acompanhar no desenvolvimento do projeto de dissertação, e com quem aprendi bastante.

Aos amigos de infância que sempre estiveram presentes durante estes 5 anos de faculdade.

Aos colegas e amigos de faculdade e às boas amizades construídas na residência de estudantes onde morei nos últimos 4 anos.

E por último um especial e incondicional agradecimento aos meus pais e ao meu irmão que sempre me apoiaram e fizeram possível realizar este sonho. A eles, um muito obrigado.

# Index

| Abstractiii                                                            |

|------------------------------------------------------------------------|

| Resumov                                                                |

| Agradecimentosvii                                                      |

| Indexix                                                                |

| List of figuresxiii                                                    |

| List of tablesxvii                                                     |

| Abbreviation and symbols xix                                           |

| Chapter 1                                                              |

| Introduction                                                           |

| 1.1. Motivation                                                        |

| 1.2. Power converter system                                            |

| 1.2.1. The power density                                               |

| 1.2.2. Standards and regulation                                        |

| 1.2.3. Requirements and specifications                                 |

| 1.3. Research goals and contributions                                  |

| 1.4. Structure of the Document                                         |

| Chapter 2                                                              |

| State of the Art                                                       |

| 2.1. Review of isolated and bidirectional DC-DC converters             |

| 2.1.1. Dual-Active-Bridge (DAB)                                        |

| 2.1.2. Three-phase dual-active-bridge                                  |

| 2.1.3. Series resonant DAB                                             |

| 2.1.4. CLLC-DAB                                                        |

| 2.1.5. Comparison of different topologies operated with soft-switching |

| 2.2. Dual active bridge topology                                       |

| 2.3. Modulations for the DAB                                           |

| 2.3.1. Phase-shift modulation                                          |

| 2.3.2. Dual-phase-shift modulation                                     |

| 2.3.3. Trapezoidal and triangular modulation                           |

| 2.3.4. Frequency Variation                                             |

| 2.3.5. Comparison of modulations                                       |

| 2.4. Semiconductor overview                                  |          |

|--------------------------------------------------------------|----------|

| 2.4.1. IGBT and MOSFET                                       |          |

| 2.4.2. The emerging technology of wide-bandgap material      | 47       |

| 2.4.3. The application of SiC in power electronics           |          |

| 2.5. Magnetics for DC-DC converter                           | 50       |

| 2.5.1. Electrical and magnetic domain                        | 50       |

| 2.5.2. Hysteresis curve                                      | 53       |

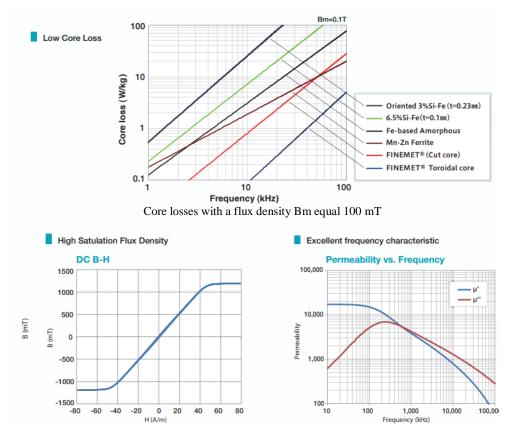

| 2.5.3. Magnetic Materials                                    |          |

| 2.5.4. Losses                                                | 58       |

| 2.6. Conclusions                                             | 58       |

|                                                              |          |

| Chapter 3                                                    | 61       |

| Converter design                                             | 61       |

| 3.1. Traditional modulation                                  | 01<br>62 |

| 3.1.1.Procedures to choose the right transformer turn rate N |          |

| 3.2. Analysis of the DAB topology neglecting the losses      |          |

| 3.3. Modeling of the DAB converter                           |          |

| 3.3.1. The equation of DAB in steady state                   |          |

|                                                              |          |

| 3.3.2. Small-signal derivation                               |          |

| 3.4. Components sizing                                       |          |

| 3.4.1. AC link inductance                                    |          |

| 3.4.2. Input and output filters                              |          |

| 3.5. Project of the HF Transformer                           |          |

| 3.5.1. Design procedure                                      |          |

| 3.5.2. Transformer design                                    |          |

| 3.5.3. Discussion                                            |          |

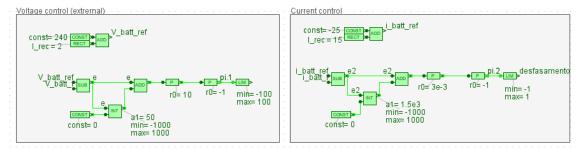

| 3.6. Controller design                                       |          |

| 3.7. Simulation in open loop                                 |          |

| 3.7.1. Magnetizing inductance                                |          |

| 3.7.2. Parameters of the simulation model                    |          |

| 3.7.3. Thermal model derivation                              |          |

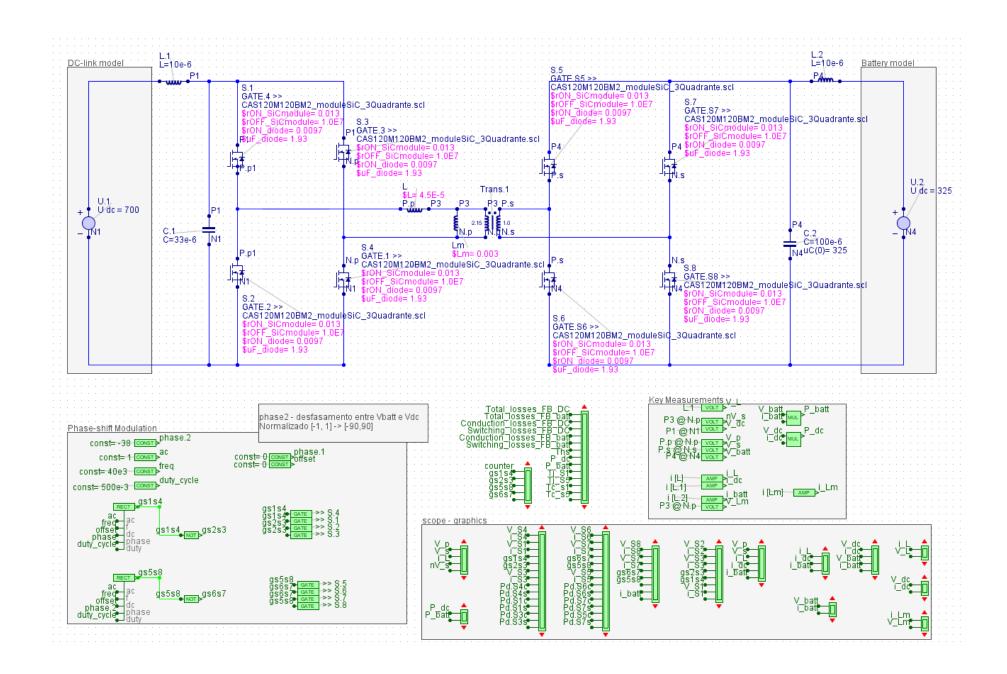

| 3.7.4. Modulation circuit - PSM                              |          |

| 3.7.5. Results of the simulation                             |          |

| 3.7.6. Discussion                                            |          |

| 3.8. Simulation in closed-loop                               |          |

| 3.9. Conclusions                                             | 105      |

|                                                              |          |

| Chapter 4                                                    |          |

| Converter - project proposal                                 | 107      |

| 4.1. Power switches                                          |          |

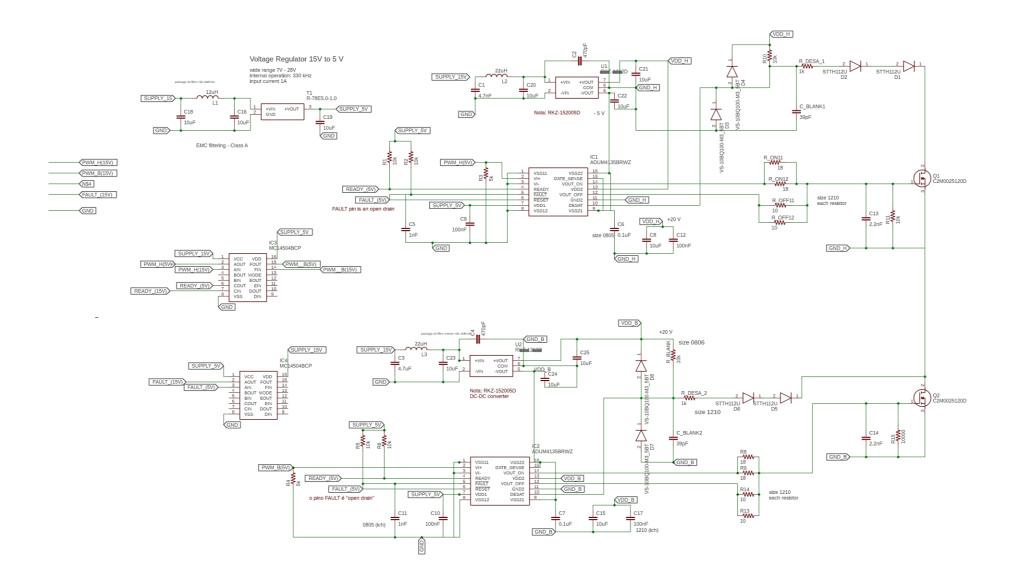

| 4.2. Gate Driver SiC MOSFETS                                 | 111      |

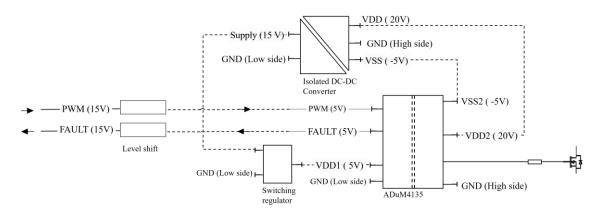

| 4.2.1. Gate driver circuit for SiC MOSFET                    |          |

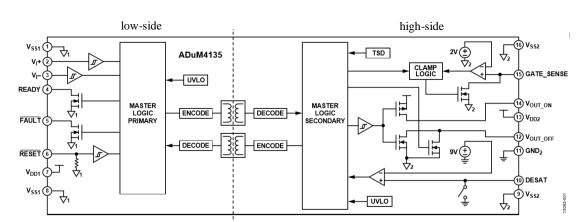

| 4.2.2. The ADuM4135 – smart driver                           |          |

| 4.2.3. Low-side of the gate driver                           |          |

| 4.2.4. High-side of the gate driver                          |          |

| 4.2.5. Power to driving a MOSFET                             |          |

| 4.2.6. Isolated DC-DC power supply and signal conditioning   |          |

| 4.3. DC capacitor and Bus-bar                                |          |

| 4.4. Proposal                                                |          |

| ·r ····                                                      | ·······  |

| Chapter 5                                                    |          |

| -                                                            |          |

| Conclusions and Future Work                                  | 127      |

|                                                              |          |

| <ul><li>5.1. Conclusions</li><li>5.2. Future work</li></ul>  | 127      |

| Appendix   |  |

|------------|--|

| References |  |

# List of figures

| Figure 2.1 - Bidirectional and isolated dual-active bridge dc-dc converter                                       | . 28 |

|------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.2 - Three-phase DAB-isolated bidirectional DC-DC converter from [4]                                     | . 29 |

| Figure 2.3 - Series resonant DAB isolated and bidirectional dc-dc converter [5].                                 | . 30 |

| Figure 2.4 - Bidirectional and isolated full-bridge CLLC, adapted from [8]                                       | . 31 |

| Figure 2.5 - Single-phase dual active bridge topology for IBDC converter                                         | . 34 |

| Figure 2.6 - Forward mode $IBatt > 0$ and $IDC < 0$ . Reverse mode $IBatt < 0$ and $IDC > 0$ .                   | . 34 |

| Figure 2.7 - Idealized operating waveforms of the DAB converter ( <i>iL</i> , <i>vpri</i> and <i>vpri</i> ), and |      |

| vpri lead vsec                                                                                                   | .36  |

| Figure 2.8 - Simplest diagram of power flow on DAB-IBDC converter with phase-shift                               |      |

| modulation. Arrows indicate the direction of energy flow in the converter.                                       | .37  |

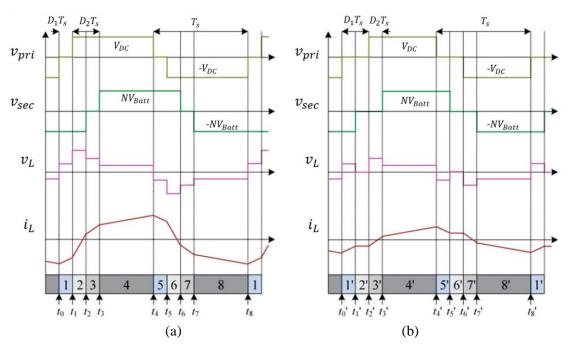

| Figure 2.9 - (a) Ideal waveform of IBDC under DPS in the condition of $0 \le D1 \le D2 \le 1$ .                  |      |

| (b) Ideal waveforms of IBDC under DPS control in the condition of $0 \le D2 \le D1 \le 1$                        |      |

| [16].                                                                                                            | .38  |

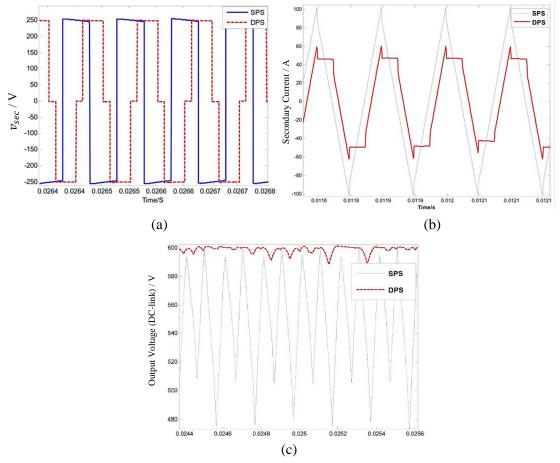

| Figure 2.10 – Comparison of control algorithms SPS and DPS. (a) Transformer secondary                            |      |

| voltage under SPS and DPS. (b) Primary current resulted by implements SPS and DPS                                |      |

| under same output power. (c) Voltage ripple for two control algorithms (same PI                                  |      |

| parameter, $C = 200 \mu F$ ) [15].                                                                               | . 39 |

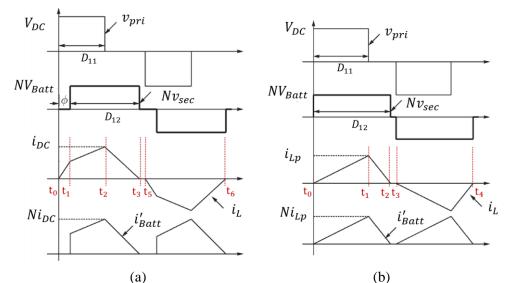

| Figure 2.11 - Ideal waveforms of the two different modulations and the power transit between                     |      |

| first H-bridge into second H-bridge. (a) Trapezoidal modulation. (b) Triangular                                  |      |

| modulation.                                                                                                      | .41  |

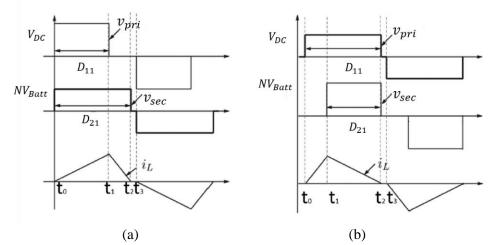

| Figure 2.12 - Key waveforms of triangular modulation. (a) TRM when $VBatt > NVDC$ . (b)                          |      |

| TRM when VDC < NVBatt                                                                                            | .42  |

| Figure 2.13 - Main application of the power device and the integration of the GaN and SiC                        |      |

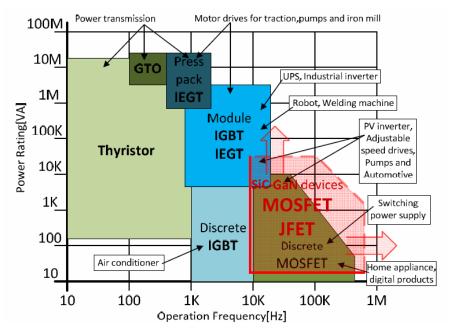

| semiconductor on the market [24]                                                                                 | .46  |

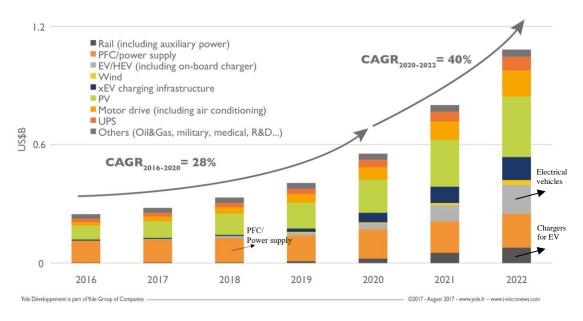

| Figure 2.14 - The SiC device in the market for the next years slip by application [27]                           | . 49 |

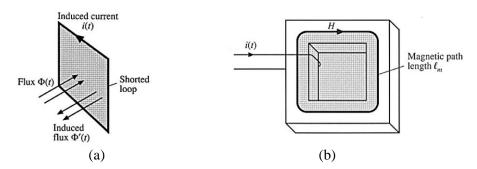

| Figure 2.15 - (a) Simple schematic that illustrates the current $i(t)$ induced by the flux $\phi(t)$             |      |

| in a short loop wire. (b) close magnetic core.                                                                   | . 51 |

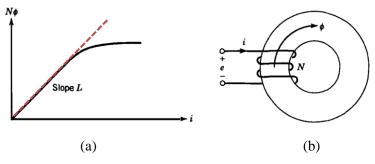

| Figure 2.16 – Self-inductance represented by L'.                                                                 | . 53 |

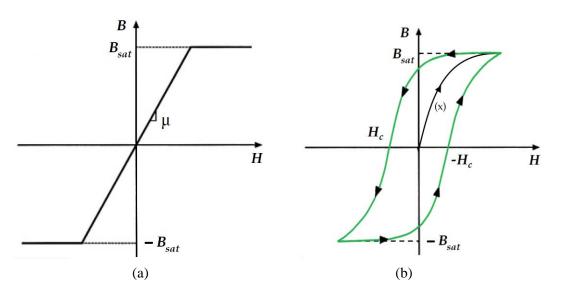

| Figure 2.17 - (a) Curve B-H characteristic of the magnetic core material by neglecting the                       |      |

| hysteresis. (b) The typical <i>B-H</i> magnetization curve                                                       | . 54 |

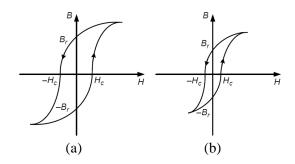

| Figure 2.18 - Hysteresis cycle for: (a) hard magnetics materials and (b) soft magnetics                          |      |

| materials[28].                                                                                                   | . 55 |

| Figure 3.1 - The main structure of the DAB converter for this project.                                           | . 61 |

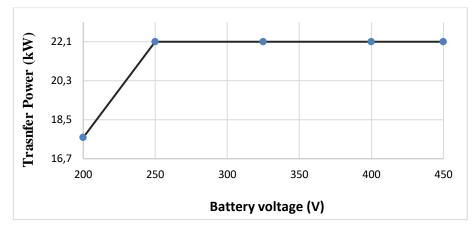

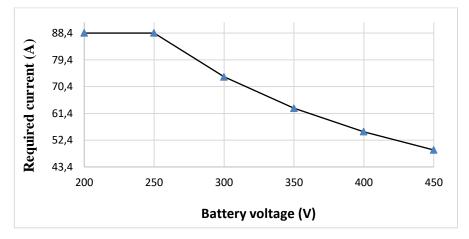

| Figure 3.2 – Power transfer as a function of battery voltage level.                                              | . 63 |

| Figure 3.3 – Required current as a function of battery voltage level                                             |      |

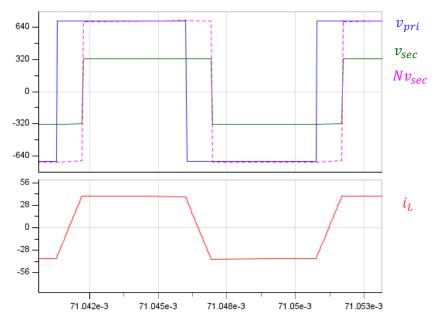

| Figure 3.4 - Waveforms vpri, vsec, and Nvsec obtained from circuit simulator under PSM                           |      |

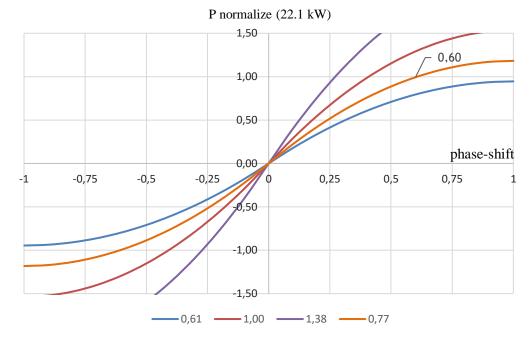

| Figure 3.5 - Relationship between transfer power and phase-shift angle                                           |      |

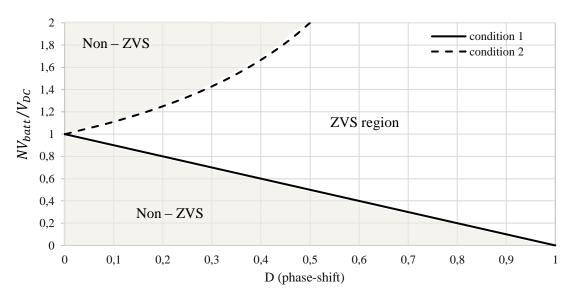

| Figure 3.6 – Definition of the soft-switching region.                                                            |      |

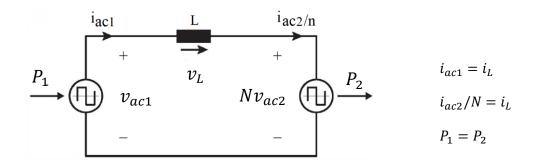

| Figure 3.7 – A general model without losses consideration.                                                       | . 67 |

|                                                                                                                  |      |

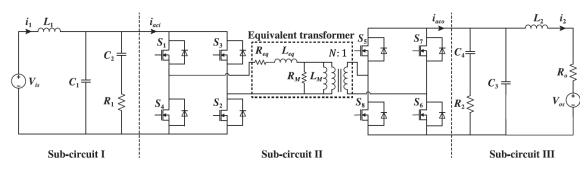

| Figure 3.8 - Circuit DAB with the main parameters represented [35]                                                                                          | 68    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

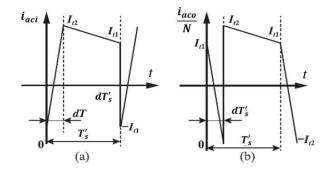

| Figure 3.9 - Input and output current in DAB. (a) Input current <i>iaci</i> in first H-bridge and (b)                                                       |       |

| output current iaco in the second H-bridge represented in a half switching period                                                                           | 70    |

| Figure 3.10 - Diagram of the system transfer function depending on the phase angle as input.                                                                |       |

|                                                                                                                                                             | 72    |

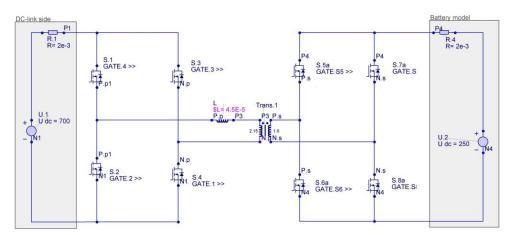

| Figure 3.11 – Simple DAB converter structure in environment simulation GeckoCIRCUITS.                                                                       |       |

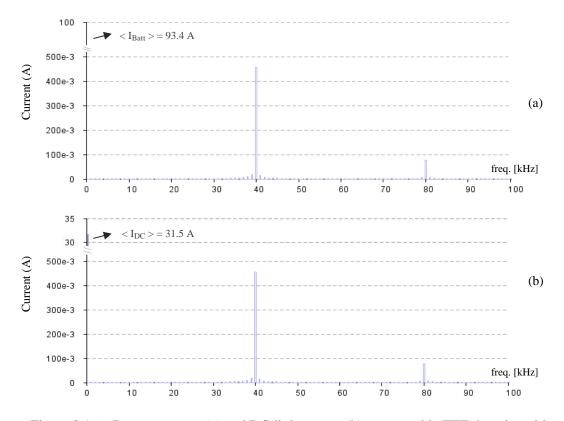

|                                                                                                                                                             | 74    |

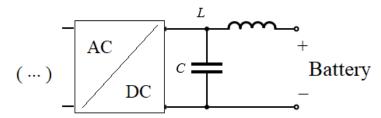

| Figure 3.12 – Typical LC structure filter.                                                                                                                  | 75    |

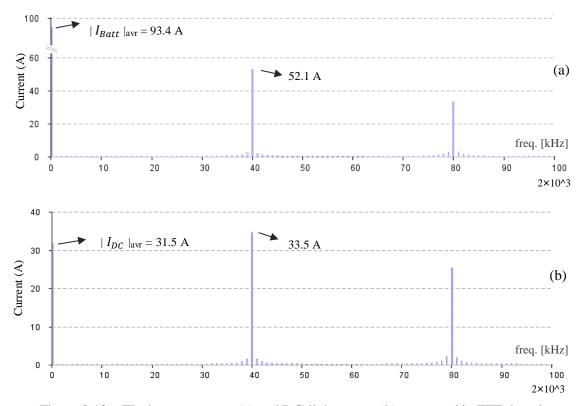

| Figure 3.13 – The battery current (a) and DC-link current (b) expressed in FFT domain                                                                       | 76    |

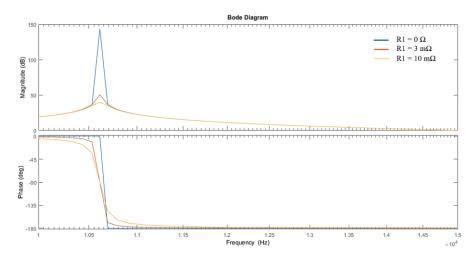

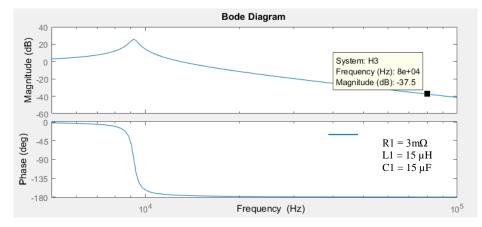

| Figure 3.14 – Frequency response of the input <i>LC</i> filter, magnitude (dB) vs frequency (Hz)                                                            |       |

| as a function of the series resistance.                                                                                                                     | 78    |

| Figure 3.15 – Frequency response of input filter <i>RLC</i>                                                                                                 | 78    |

| Figure 3.16 – Battery current (a) and DC link current (b) expressed in FFT domain, with <i>RLC</i>                                                          |       |

| filters                                                                                                                                                     |       |

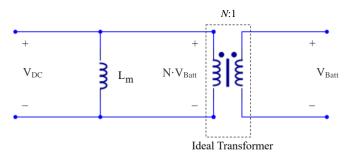

| Figure 3.17 – The transformer model used in the simulation with a magnetizing inductance                                                                    |       |

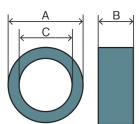

| Figure 3.18 – Shape of the nanocrystalline core selected.                                                                                                   |       |

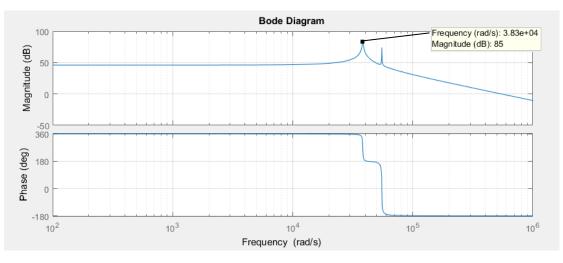

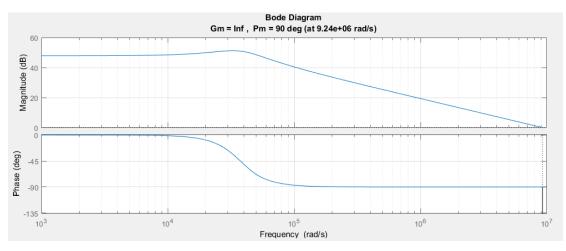

| Figure 3.19 – Bode plot representation of the output transfer function with $D=0.5$ ,                                                                       |       |

| input/output filters and other non-idealities.                                                                                                              |       |

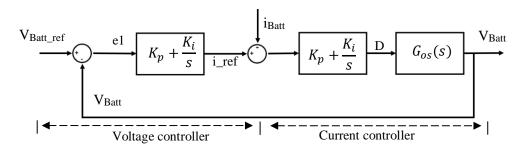

| Figure 3.20 – Purposed closed-loop controller for DAB converter                                                                                             |       |

| Figure 3.21 – The unit step response of the system in open-loop at 40 kHz.                                                                                  |       |

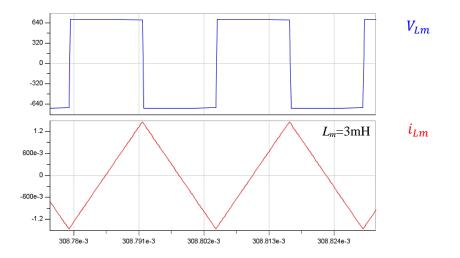

| Figure 3.22 – Waveform of the magnetizing current on <i>Lm</i> from the simulation.                                                                         |       |

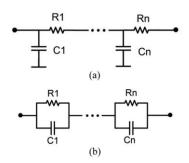

| Figure 3.23 – Equivalent thermal network. (a) Cauer model and (b) Foster model respectively                                                                 | . / 1 |

| [38].                                                                                                                                                       | 93    |

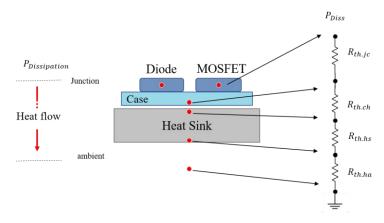

| Figure 3.24 – Equivalent thermal model resistance in a network configuration.                                                                               |       |

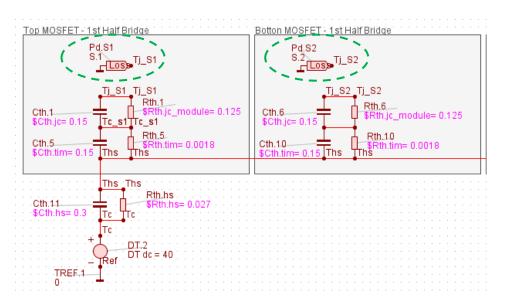

| Figure $3.25$ – Part of the thermal model to the MOSFET and the heatsink designed in                                                                        |       |

| GeckoCIRCUITS® environments.                                                                                                                                |       |

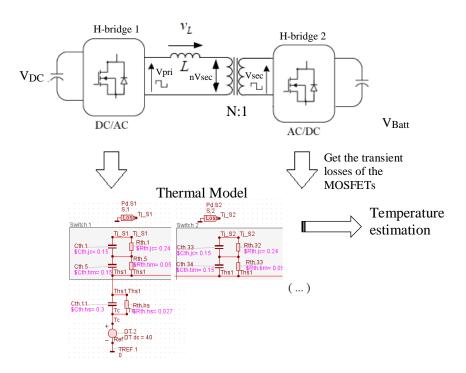

| Figure 3.26 – Functional diagram of the implemented thermal model.                                                                                          |       |

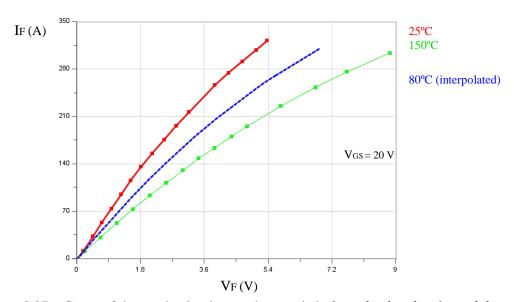

| Figure 3.27 – Curve of the conduction losses characteristic from the datasheet's module                                                                     | .95   |

| CAS120M12BM2 set in the circuit simulator                                                                                                                   | 05    |

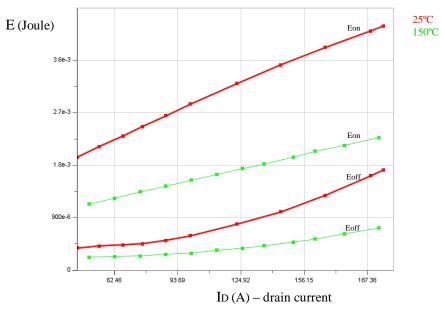

| Figure 3.28 – Curve of the switching losses characteristic at 25°C and 150°C from the                                                                       |       |

| datasheet's module CAS120M12BM2, separated by turn-on and turn-off losses.                                                                                  | 05    |

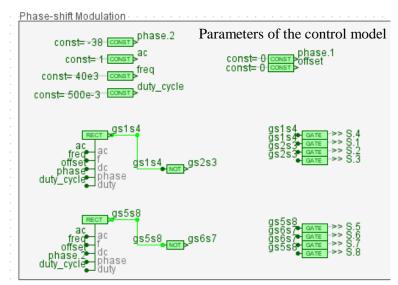

| Figure 3.29 – The control model to implement the traditional phase-shift modulation                                                                         |       |

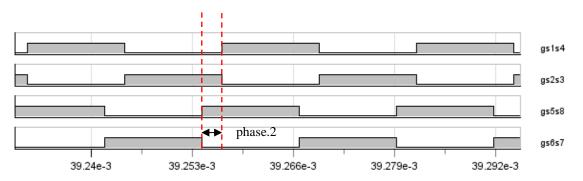

| Figure 3.30 – PWM signals under single phase-shift modulation.                                                                                              |       |

| Figure 3.30 – F with signals under single phase-sinit modulation. Figure 3.31 – Simulation of the DAB under PSM at 40 kHz, in nominal power and $D = 0.607$ | .90   |

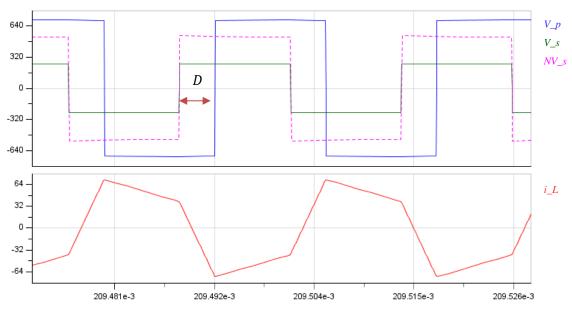

|                                                                                                                                                             | 00    |

| meaning 54.7° of phase-shift: steady-state regime.                                                                                                          | 98    |

| Figure 3.32 - Simulation of the DAB under PSM at 40 kHz, in nominal power and $D = 0.607$ :                                                                 | 00    |

| steady-state regime.                                                                                                                                        | 98    |

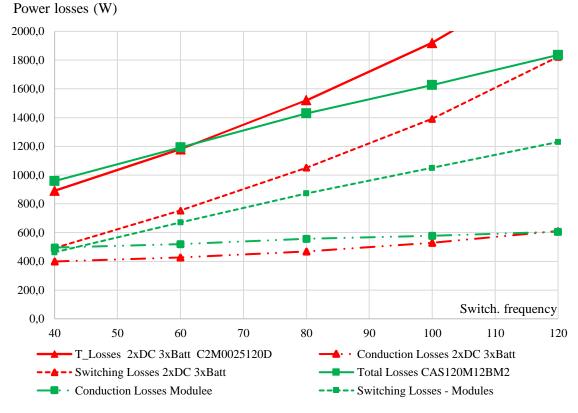

| Figure 3.33 – Power losses on semiconductors measured from the simulation some different                                                                    |       |

| switching frequencies at nominal transferred power with 250 V on the battery                                                                                | 00    |

| (discharging operation) for two different power switch solutions.                                                                                           | 99    |

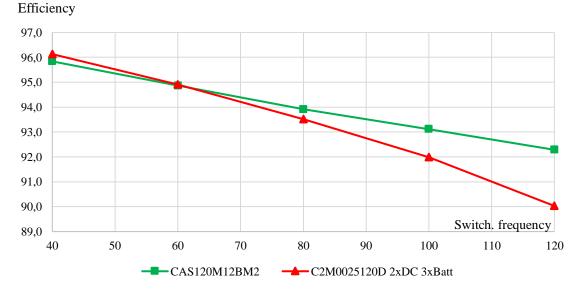

| Figure 3.34 – Efficiency comparison between the module and discrete MOSFETs for DAB                                                                         |       |

| circuit performed at nominal transferred power, in a discharging mode with 250 V on                                                                         |       |

| the battery.                                                                                                                                                |       |

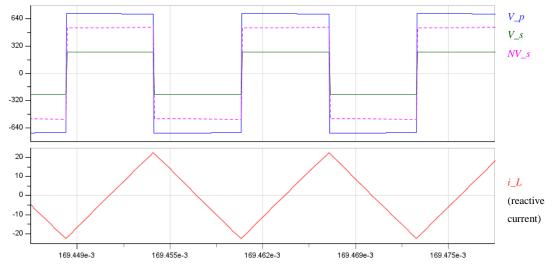

| Figure 3.35 – The shape of the voltage applied to the transformer terminals and the                                                                         |       |

| transformer current drawn with zero phase-shift                                                                                                             | 101   |

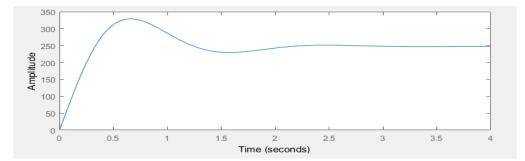

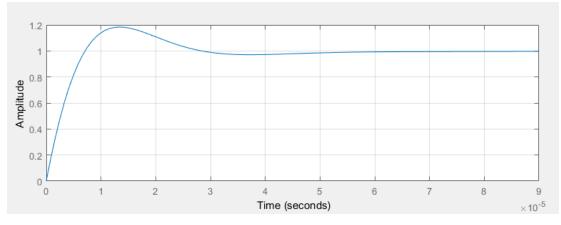

| Figure 3.36 -Step unit response of the second-order system with a PI controller in closed-                                                                  |       |

| loop                                                                                                                                                        | 104   |

| Figure 3.37 – Bode diagram of the output transfer function with $D = 0.4$ , and includes                                                                    |       |

| input/output filter, damping resistors, and other non-idealities                                                                                            | 104   |

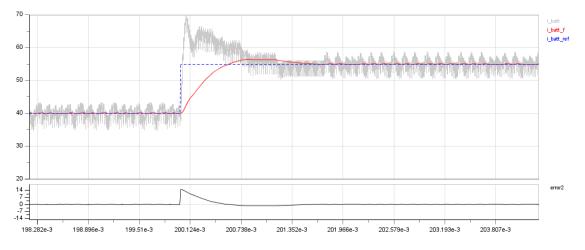

| Figure 3.38 – Dynamic response of the DAB converter to a change of the discharging current                                                                  |       |

| imposed to battery following a reference, at 40 kHz and a battery voltage of 250V                                                                           | 104   |

|                                                                                                                                                             |       |

| Figure 4.1 – Block Diagram of the gate driver with the representative internal function                                                                     |       |

| Figure 4.2 – Example of circuit driver application.                                                                                                         |       |

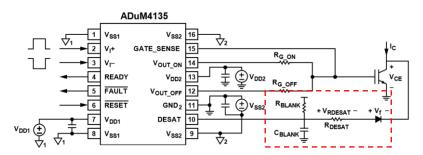

| Figure 4.3 – Desaturation circuit. Desaturation circuit is adapted to the project application                                                               | 118   |

| Figure 4.4 – Example of a desaturation events timing diagram, from datasheet's gate | driver118 |

|-------------------------------------------------------------------------------------|-----------|

| Figure 4.5 - Safe operation from datasheet's C2M0025120D                            | 119       |

| Figure 4.6 – Timing delay vs $R_{G(ext)}$                                           |           |

| Figure 4.7 – Diagram of circuit gate driver designed for one single MOSFET.         |           |

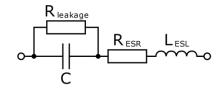

| Figure 4.8 – Capacitor with detail parameters.                                      |           |

|                                                                                     |           |

# List of tables

| Table 1 – Specifications and main requirements.                                                              | .23 |

|--------------------------------------------------------------------------------------------------------------|-----|

| Table 2 Classification of IBDC Topology based on the number of switched [3].                                 |     |

| Table 3 - Comparison of single-phase and three-phase DAB-IBDC [3].                                           | .29 |

| Table 4 Comparison of various topologies operated with soft-switching. Conclusion based on                   |     |

| [4]                                                                                                          | .33 |

| Table 5 – Results of changing the FS from its design value.                                                  | .43 |

| Table 6 – Main difference between the algorithm studied.                                                     | .45 |

| Table 7 - Properties of wide-bandgap material compared to the silicon material [26]                          | 48  |

| Table 8 – Soft magnetic materials and their properties [28]                                                  | 56  |

| Table 9 – Physical parameters of Sof Magnetics Materials [31].                                               | 57  |

| Table 10 – Magnetic parameters of soft magnetic materials[31].                                               | 57  |

| Table 3.1 – Voltage ratio with N=2.15.                                                                       | .65 |

| Table 3.2 – Filter inductance in order to the switching frequency.                                           | .73 |

| Table 3.3 – Two nanocrystalline toroidal core with different size and own characteristics                    | 81  |

| Table 3.4 – Nanocrystalline core losses at the different operating frequency for flux density                |     |

| of 100 mT                                                                                                    | 81  |

| Table 3.5 – Different configuration of npri: nsec and the respective primary magnetizing                     |     |

| inductance, considering the transformer operation at 80 kHz                                                  |     |

| Table 3.6 – Winding parameters for different scenarios of turn ratio.                                        | 85  |

| Table 3.8 – Estimation of the magnetic field applied to the toroidal nanocrystalline core and                |     |

| expected magnetizing current ripple with the converter operating at 80 kHz, for two                          |     |

| different winding turns                                                                                      | 86  |

| Table 3.8 - Copper losses expected for both side of the transformer in a different                           |     |

| configuration of turn ratio.                                                                                 |     |

| Table 3.9 – Transformer design with a nanocrystalline core                                                   |     |

| Table 3.11 – Parameters of the Input and output filters and respective requirements                          | .90 |

| Table 3.12 – Circuit specification of the detailed DAB DC-DC converter simulated in                          | ~ ~ |

| GeckoCIRCUITS® environments                                                                                  | 92  |

| Table 3.12 – Average temperature estimated in Celsius from the thermal model with discrete                   |     |

| MOSFET                                                                                                       | 00  |

| Table 3.13 - Average temperature estimated from the thermal model with MOSFET module.                        | 100 |

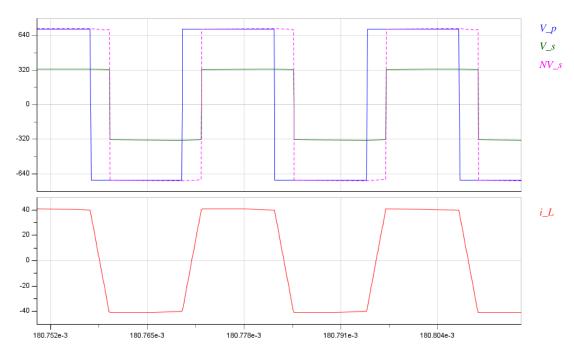

| Table 3.15 – Results from a simulation of the DAB converter at rated power, 40 kHz and                       | 100 |

| VBatt = 250 V.                                                                                               | 01  |

| Table 3.15 - Average temperature obtained from the thermal model                                             |     |

| Table 3.17 - Reactance of the inductor sized early.       1                                                  |     |

| Table 3.17 – Reactance of the inductor sized earry.         Table 3.18 – PI controller parameters.         1 |     |

| Table 4.1 – Key parameters of SiC MOSFET from different manufacturers                                        |     |

| Table 4.2 – Discrete MOSFETs available and its specifications                                                |     |

| Table 4.2 – Gate driver available and intrinsic parameters and functions                                     |     |

| 1 a 0 0 + 3 $- 0 a 0 0 1 v 0 a variable and mutuiste parameters and runchous 1$                              | -14 |

| Table 4.4 – Truth table, from the gate driver datasheet.                               | .114 |

|----------------------------------------------------------------------------------------|------|

| Table 4.5 - Components presents in the desaturation circuit.                           | .119 |

| Table 4.6 - Gate resistance and switching times.                                       | .121 |

| Table 4.7 – Power dissipation as a function of the switching frequency.                | .122 |

| Table 4.8 – Isolated DC-DC converter supply.                                           | .122 |

| Table 4.9 – Filtering parameters and specification for each H-bridge                   |      |

| Table 4.10 - Parameters and specification of the proposal isolated DC-DC DAB converter |      |

# Abbreviation and symbols

### Lists of abbreviations

| AC       | Alternating Current                             |

|----------|-------------------------------------------------|

| AWG      | Standardized American Winding Gauge             |

| DAB      | Dual-Active-Bridge                              |

| DC       | Direct Current                                  |

| DPS      | Dual Phase-Shift modulation                     |

| SPS      | Single Phase-Shift                              |

| Eoff/Eon | Switching turn-off or turn on losses respective |

| EMI      | Electromagnetic interference                    |

| EV       | Electric Vehicle                                |

| FFT      | Fast Fourier Transformer                        |

| GaN      | Gallium Nitride                                 |

| HF       | High Frequency                                  |

| IBDC     | Isolated Bidirectional DC Converter             |

| IEC      | International Electrotechnical Commission       |

| Llk      | Leakage Inductance                              |

| PCB      | Printed Circuit Board                           |

| PFC      | Power Factor Correction                         |

| PSM      | Phase-Shift modulation                          |

| Rth.TIM  | Thermal Interface Material Resistance           |

| Rth.ch   | Heatsink Thermal Resistance                     |

| Rth.jc   | Junction to Case Thermal Resistance             |

| Si       | Silicon element                                 |

| SiC      | Silicon Carbide element                         |

| SPS      | Single Phase-Shift (same as PSM)                |

| TRM      | Triangular modulation                           |

| TZM | Trapezoidal modulation     |

|-----|----------------------------|

| Ths | Heatsink temperature       |

| Tj  | Junction Temperature       |

| UPS | Uninterrupted Power Supply |

| ZCS | Zero-Current-Switching     |

| ZVS | Zero-Voltage-Switching     |

|     |                            |

## Lists of symbols

| А                                    | Ampere                                                                 |

|--------------------------------------|------------------------------------------------------------------------|

| A <sub>c</sub>                       | Cross-sectional area of the magnetic core                              |

| Aw                                   | Conductor Cross-sectional Area                                         |

| B                                    | flux density                                                           |

| B<br>B <sub>max</sub>                | Maximun Flux Density                                                   |

| B <sub>max</sub><br>B <sub>sat</sub> | Saturation Flux Density                                                |

| δ                                    | Phase-shift in radians                                                 |

| D <sub>1</sub>                       | Phase-shift of diagonal switches normalized                            |

| D <sub>1</sub><br>D <sub>2</sub>     | Phase-shift between two output voltage of H-bridge at transformer side |

| $f_{SW}$                             |                                                                        |

| Jsw<br>Hz                            | Switching frequency<br>Hertz                                           |

| Hz<br>H <sub>c</sub>                 | Coercive force                                                         |

| II <sub>c</sub>                      |                                                                        |

| -                                    | Current Density Magnetics path length core                             |

| l <sub>c</sub>                       | Magnetics path length core                                             |

| L <sub>m</sub>                       | Magnetizing inductance                                                 |

| Ν                                    | Turn ratio                                                             |

| n <sub>pri</sub>                     | Number of turns in the primary side                                    |

| P <sub>cu</sub>                      | Copper or winding losses                                               |

| $P_c, P_{fe}$                        | Core losses                                                            |

| ${\mathcal R}$                       | Electromotive force                                                    |

| V                                    | Volt                                                                   |

| V <sub>Batt</sub>                    | Voltage across the battery                                             |

| V <sub>DC</sub>                      | DC-link voltage                                                        |

| $\mu 0$                              | free air permeability                                                  |

| μr                                   | relative permeability                                                  |

| $ ho_W$                              | Electrical Resistivity                                                 |

| W                                    | Angular frequency (rad/s)                                              |

|                                      |                                                                        |

## Chapter 1

# Introduction

In this chapter, the motivation and main goals of this dissertation theme are presented. The chapter begins with a presentation of the proposed dissertation, followed by a description of objectives to be achieved and finally the structure of the document.

### 1.1. Motivation

Nowadays the demand for electric vehicles is growing and has been a challenge for the power electronics field that needs to be continuously looking for innovative solutions in order to make more compact and robust converters with the best efficiency.

Since the beginning of this century, the transportation systems are continually changing and innovating. Especially in cities, the electrification of transports is a priority issue due to high pollution levels and noise. This topic has been discussed, and there are some companies that seek innovation in this sector, as Mercedes-Bens which intends to have an electric version of each car model until 2022 [1]. Countries are concerned in reducing emissions, and it is consensual the adoption of electrical vehicles: e.g., France has the plan to ban the sale of cars with internal combustion engines – conventional engines – until 2040 [2]. Norway is more ambitious and pretends in 2025 sell only electric vehicles.

AddVolt is a Portuguese company who developed a solution targeted to reduce fuel consumption, noise and pollutant emissions in heavy duty vehicles. This technology allows recovering energy during braking or deceleration by installing an electrical generator in the truck. The generated energy is stored in a battery pack and then used to power a secondary electrical system

Introduction

that is responsible for the refrigeration of "goods". This solution is mainly focused on the refrigerated transportation sector, where the traditional diesel motor is used to power the refrigeration system. A reduction of  $CO_2$  and noise levels are expected along with reduced maintenance.

Increasingly, the population's awareness and political pressures have led to the adoption of renewable energies and this has changed for example the way we move, with the adoption of electric vehicles. Power electronics play an important role, in particular with DC-DC bidirectional power converters in various applications ranging, as the electric vehicle chargers. The interface between the electrical generator, the battery pack, and the secondary electrical system is implemented by power electronics converters. Bidirectional AC-DC and DC-DC conversion stages are required to control the power flow in both direction and to make that, with high efficiency, an advantage technique modulation is approached.

Therefore, the study of this dissertation has the objective of improving the prototype of bidirectional DC-DC converter already used in the company, making it more compact and lighter.

#### **1.2.** Power converter system

The power electronics converters are essential components for the electrical system of the truck. The purpose of energy converters is to convert electrical energy from one form to another in an appropriate manner, AC-DC, DC-DC, or just by changing the voltage or frequency level, which ultimately can result in a combination of these.

#### 1.2.1. The power density

When a power converter is required to increase the power rate, the intrinsic components, mainly the passive filters, they are usually large due to the high current which must be archived. The power losses increase when a converter is working in high current. The high switching frequencies bring other issues regarding the electromagnetic interference (EMI), and the EMI filters will be larger to face this situation. With the reason presented before, it is difficult to increase the power rate per volume of equipment. The converter power density is a metric of power per mass/volume, and it is limited by the component sizes. Therefore, it is a challenge for design engineers to find solutions which allow to improve and make the converter with high power density and the best efficiency.

#### 1.2.2. Standards and regulation

The respective standard regulations applicable to the mode of operation of the isolated DC-DC converter are summarized:

- IEC 61800-3:2017: EMC requirements and specific test methods;

- IEC 61800-5-1:2007: Safety requirements Electrical, thermal and energy.

These standards are applicable to this type of system and they are the same as those applied to the adjustable speed power drive systems.

#### 1.2.3. Requirements and specifications

The specifications and main requirements for the bidirectional and isolated DC-DC converter are listed in Table 1.

| Secondary voltage, battery side (OPT1) | 200-450 V       |

|----------------------------------------|-----------------|

| Secondary voltage, battery side (OPT2) | 120-175 V       |

| Primary voltage, DC-link side (OPT1)   | 700 V           |

| Primary voltage, DC-link side (OPT2)   | 400 V           |

| Maximum output power                   | 22.1 kW         |

| Galvanic isolation                     | Yes             |

| Bidirectional power flow               | Yes             |

| Power density                          | $\geq$ 2.0 kW/l |

| Overvoltage and overcurrent protection | Yes             |

| Cooling                                | Air cooling     |

Table 1 – Specifications and main requirements.

This converter is intended to be used with three-phase and single-phase inverters. Therefore, and in order to obtain a versatile conversion system, two different operating ranges for the battery and inverter sides are considered depending if the system is working in a three-phase (OPT1) or single-phase (OPT2) configuration. The battery pack for three-phase configuration ranges from 200 to 450 V. In turn, the voltage should be controlled in the 120 to 175V range for single-phase systems. A galvanic isolation between two DC bus is a mandatory requirement. The DC-link voltage in three-phase configuration is settled at 700 V, while for single-phase configurations 400V are used.

Introduction

#### **1.3. Research goals and contributions**

The power electronics have been growing for the past few decades due to industrial demand, so making systems more compact, more efficient and more robust has become determinant for the industry. Many counties are concerned with the environmental pollution, and it has become a central trigger for engineers to find new technologies, in order to enable the use of clean and sustainable energies in a more efficient way. Gallium Nitride (GaN) and Silicon Carbide (SiC) materials are the example of recent tecnologies which can enable this. During many years, the Silicon (Si)-based semiconductors were largely used as the leading solution for power application due to its well known mature technology and their low cost. However Si-based semiconductors have limited switching frequency operation which is not suitable for high power applications where high power density is required. A brief overview of that material will be presented in the next chapter, emphasizing their characteristics and advantages.

The main objective is to design and implement an isolated high-power density bidirectional dc-dc converter, improving the existing prototype in the company. An overview of bidirectional dc-dc converter topologies is presented in state of the art as well as the main modulation techniques. The mathematical model of the converter is also an essential design requirement for performing closed-loop simulations which allows a better approximation of the system to be implemented. The simulations are performed in a graphical environment via GeckoCIRCUITS® that will enable to support and validate the theoretical study.

Considering this, it is presented below a list of the specific primary goals of the dissertation:

- Revision of the state of the art of bidirectional and isolated dc-dc converters (IBDC);

- A detail analysis of dual-active-bridge (DAB) topology.

- The study and comparison of the most used modulation methods for the DAB

- Phase shift modulation

- o Dual phase-shift modulation

- Trapezoidal modulation

- Frequency modulation

- Simulation in GeckoCIRCUITS® software of DAB topology operating with the selected modulation,

- Design and implementation of the bidirectional and isolated dc-dc converter responsible for the interface between the battery pack and the DC link coupled at the inverter side.

- It is expected to have experimental result in open-loop and closed-loop operating modes.

### **1.4. Structure of the Document**

The first chapter presents the main objectives of the dissertation. Emphasis is given to power converters and their importance in electronic systems is explained. The converter requirements are also presented.

The second chapter focusses in the literature review of isolated and bidirectional dc-dc converter topologies. A review of the common and advanced modulation techniques used in DAB converters is done. Advantages and disadvantages are highlighted.

The chapter 3 demonstrates the mathematical model of the converter and the entire modeling process is documented, followed by component design, control design, and simulation in openloop and the closed-loop mode of operation. A thermal model for power semiconductors is presented in order to estimate the temperature and losses in the active components.

Chapter 4 covers the research of available power semiconductors with SiC technology. Main considerations for driving circuit, the isolation between the low and high side of the driver is presented. A design of a circuit to a half bridge with SiC MOSFETs are presented and explained the main stage of the implementation. At the end of the chapter, a DAB solution is presented, and include active and passive components chosen.

The final chapter 5 make an overview of the project and suggestion for future works.

## **Chapter 2**

## State of the Art

This chapter presents the revision of different topologies of power converters for isolated bidirectional DC converter and manly comparison between those topologies with the soft switching operation.

### 2.1. Review of isolated and bidirectional DC-DC converters

In the present section, the isolated and bidirectional DC-DC topologies that result from research and study based on literature support are presented. The advantages and disadvantage of those topologies are also discussed.

A review of IBDC topologies are presented in [3] and the classification is based on the number of switches that are used in the circuit. As shown in Table 2, there are a considerable number of topologies of IBDC with a different configuration. The typically single DAB has eight switches and compares to the four-switches topology like dual-half-bridge. In turn, the DAB has the double of power capacity and the current stress is half of each transistor. This is a great feature in using DAB tropology for high power application. The ripple frequency for push-pull, half-bridge and full-bridge converters is two times high than the switching frequency.

| Classification    | Dual-switches                            | Three-<br>switch    | Four-switch                                                                          | Five-<br>switch             | Six-switch           | Eight-switch           |

|-------------------|------------------------------------------|---------------------|--------------------------------------------------------------------------------------|-----------------------------|----------------------|------------------------|

| Typical<br>models | dual-flyback,<br>dual-Cuk,<br>Zeta-Sepic | forward-<br>flyback | dual-push-pull,<br>push-pull-for-<br>ward,<br>push-pull-flyback,<br>dual-half-bridge | full-<br>bridge-<br>forward | half-full-<br>bridge | dual-active-<br>bridge |

#### 2.1.1. Dual-Active-Bridge (DAB)

Most recent years, the technological advancements in power devices and magnetic materials (mainly good results obtained in use silicon carbide - SiC - and gallium-nitride - GaN - material on power device) have made DAB-IBDC viable for eliminating bulky and heavy LF transformers from power conversion systems [3].

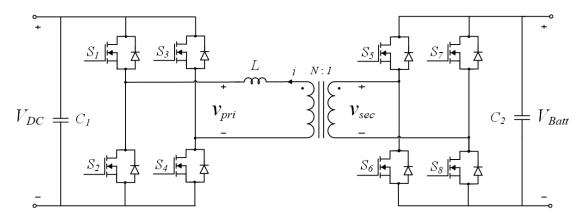

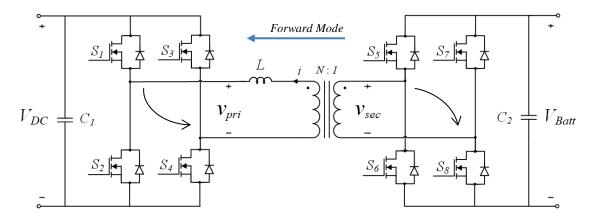

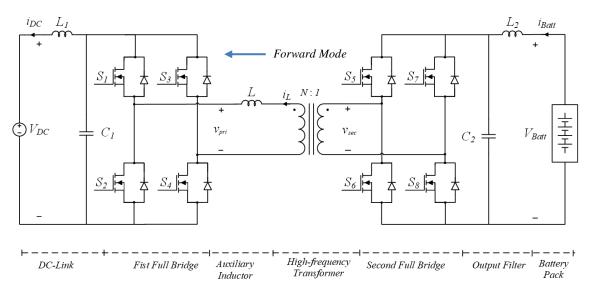

The topology shows in Figure 2.1 is known as single dual-active-bridge. The DAB was firstly introduced in 1991 [4] for high-power applications. The present circuit has two full bridge with H configuration and a voltage  $V_{DC}$  and  $V_{Batt}$  are applied to the first and second output side of respective H-bridge. The two bridges are coupled with a high-frequency transformer and this is an important component in the circuit since provides a galvanic isolation between the battery pack and the inverter. Moreover, a high-frequency operation allows to reduce the size of the transformer, so it's less bulky and heavy compared to the low-frequency transformer, also known as line-frequency transformer. The leakage inductance is a characteristic of the transformer for store and transfer energy.

The transfer of energy is obtained by changing the angle of phase between primary and secondary voltages applied to the transformer or varying the duty-cycle to obtain the desired power flow. More detail for the operation mode of DAB with soft-switching will be presented in section 2.3. along with other modulation techniques.

Figure 2.1 - Bidirectional and isolated dual-active bridge dc-dc converter.

#### 2.1.2. Three-phase dual-active-bridge

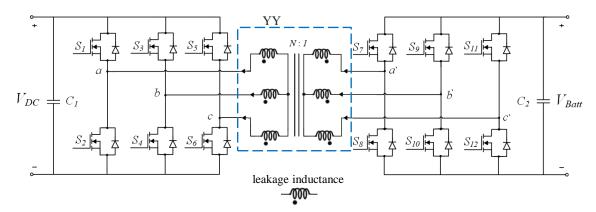

Certain applications require high power capacity, and in this way, multiphase converters are used. The simple three-phase DAB configuration is shown in

Figure 2.2. The first topology of a bidirectional DC-DC converter operating as three-phase dual-active-bridge was implemented in 1991 [4] and the AC three-phase transformer has a YY structure and the leakage inductance  $L_{lk}$  in each phase represented in the Figure 2.2 was used as the energy transfer element.

Figure 2.2 - Three-phase DAB-isolated bidirectional DC-DC converter, topology adapted from [4].

This circuit allows the energy transit in both directions, like the single DAB, between two inverting three-phase bridges through the phase-shift modulation. The switching signals for the transistors have a 50% duty cycle. An overview of the comparison between single-phase and three-phase DAB-IBD is shown in Table 3 for an application of a power transmission at 50 kW, with a  $V_{Batt} = 200$  V and output voltage of  $V_{DC} = 2000$  V. The values for the main variables resulted from the equations and curves presented in [4].

| Converter    | Number of switches | Peak current<br>A | Peak voltage<br>V | Transformer<br>kVA | Cap RMS<br>current/ A |  |

|--------------|--------------------|-------------------|-------------------|--------------------|-----------------------|--|

| Single-phase | 8                  | 297.6             | 2000              | 56.3               | 12.9                  |  |

| Three-phase  | 12                 | 293.5             | 2000              | 55.7               | 4.8                   |  |

Table 3 - Comparison of single-phase and three-phase DAB-IBDC [3].

With the analysis of Table 3, the transistors of the 3-phase converter topology have a slight reduction of current stress when compared with the single-phase topology, in column three of the table. Thus, for the same nominal voltage, the current per phase is smaller in the three-phase topology for each switch. Another feature is the ripple frequency in the DC-link current, second-ary side, it is three times the switching frequency instead of the double frequency on single DAB topologies. The total number of active devices – twelve transistors – is a disadvantage in the bidirectional three-phase converter, so more power and devices are required that increase the size and price for this circuit topology. Another disadvantage is the complex structure that not make possible building a three-phase symmetrical transformer with identical leakage inductances in each phase [3].

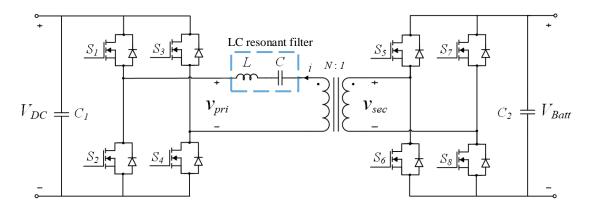

#### 2.1.3. Series resonant DAB

In Figure 2.3, the series resonant *LC*-type topology is shown. The circuit consists of a resonant tank formed by an inductor and an additional capacitor, which is the main difference compared to the single DAB converter configuration. Both the magnetic elements present in the system, inductor and capacitor, as well as the high-frequency transformer, are responsible for the energy transfer through the front-to-front converter.

Like the traditional dual-active-bridge approached described in subsection 2.1.1 it is possible to operate the *LC*-type with higher frequency and efficiency due to their advantages of operation [3]. A single-phase-shift modulation method is proposed in [5] to control the resonant series DAB converter. The active power is controlled by the only one adjustable degree of freedom– the phase-shift between the secondary and primary voltage of the high-frequency transformer. The transistors on the two H-bridges are driven with 50% duty cycle under the traditional phase-shift. For wide changes in load or supply voltage, all switches of both bridges of converter may work in zero-voltage-switching (ZVS) or zero-current-switching (ZCS) [5] renewable generation systems. The ZVS could be implemented for primary side switches and ZCS for secondary side switches [3], when the power flow is done from the primary bridge (rectifier bridge) into the secondary bridge (rectifier).

Figure 2.3 – Series resonant DAB isolated and bidirectional dc-dc converter [5].

The two IBDC topology analyzed in section 2.1.1 e 2.1.2 have intrinsic electromagnetic interference (EMI) created by rectangular waveforms of voltages which crossed through winding on both sides of the HF transformer. The EMI levels impose limits on the sizing of magnetic components, and a simple increase of switching frequency of devices to compensate that limitation is not seen as a viable solution since the switching losses increase.

The topology in Figure 2.3 has the disadvantage of being constituted by additional resonant elements compared to the traditional DAB topology, which results in increased cost and size.

#### 2.1.4. CLLC-DAB

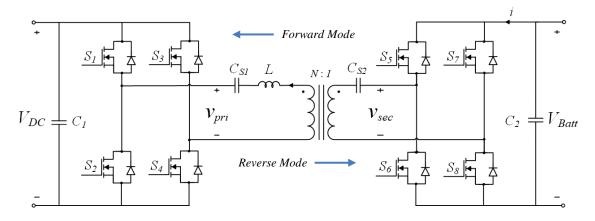

The dual-active-bridge with CLLC resonant tank has "high power density, high efficiency, buck/boost capability, and controllable bidirectional power transfer" [6]. These advantages make the converter a candidate for the implementation of bidirectional charging systems in hybrid and electric vehicles. An example of bidirectional resonant converter for battery charger application is presented in [7].

The DAB with a series-parallel CLLC tank resonant was proposed in [8] and a detail principal operation is also presented. The power transit in both directions is guaranteed by a variable frequency modulation. Looking to the Figure 2.4, in forward mode, the switches of the second bridge (been an inverter for this operation mode) are driven by 50% of the duty cycle in order to generate AC power, and the switches of the first bridge (rectifier) are turned OFF and the transferred power is rectified by the antiparallel diodes of the power switches [3]. The circuit structure is illustrated in Figure 2.4.

Figure 2.4 - Bidirectional and isolated full-bridge CLLC, adapted from [8].

The converter represented in Figure 2.4 is an asymmetric resonant bidirectional converter. The resonant network is represented by  $C_{s1}$  and inductance *L* in primary side and  $C_{s2}$  in the secondary side of the transformer. A soft-switching is implemented to eliminate the switching losses and reducing the electromagnetic interference [8]. When the converter operate in forward mode, the soft-switching is done in two ways by the zero-voltage-switching (ZVS) operation for the inverting stage (second bridge), and by the zero-current-switching (ZCS) operation of the rectifier side, at the first bridge [8]. The ZVS can be implemented in the MOSFETS semiconductors if the frequency of operation of the drive is performed below the resonant frequency. This imposed condition limits the sizing of the elements of the resonant tank. The detailed analysis of the mode of operation with soft-switching technique is presented in the literature [3, 6, 8].

#### 2.1.5. Comparison of different topologies operated with soft-switching

In all section 2.1. the mainly isolated and bidirectional topologies DC-DC along with the analysis of structure and operation with a soft-switching mode for each one was presented.

By the analysis of Table 4 is verified that for different topologies studied in previous sections, different control strategies are required. The soft-switching region of the CLLC topology is wider compared to the other DAB circuits particularly at light load conditions [6]. For the resonant topologies, series resonant and CLLC-DAB asymmetric, the control computing times increase due to the complexity of the converter that is a result of increasing system order [9]. The frequency modulation implemented in CLLC resonant converters increase the control complexity and this topology requires more resonant elements that increase the size and the cost of all converter [3]. In relation to the three-phase DAB, from the view of the filter, the frequency ripple of input/output voltage and current are three times higher than the switching frequency [10] and this is an advantage in terms of the size of the filter since the filter value is smaller due to the imposed high-frequency.

| Converter                         | Resonant<br>network<br>element | Power<br>control          | Drive                                                                            | Soft-switching charac-<br>terization                                          | Soft-<br>switching<br>range | Fre-<br>quency<br>output | Bidirec-<br>tional tran-<br>sition speed | Complexity<br>of imple-<br>mentation |

|-----------------------------------|--------------------------------|---------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|--------------------------|------------------------------------------|--------------------------------------|

| Dual-active<br>Bridge             | No                             | Phase-shift<br>modulation | All switches are driven by 50% of duty-cycle                                     | ZVS for few switches                                                          | Narrow                      | Double                   | Fast                                     | low                                  |

| Three-phase<br>DAB                | No                             | Phase-shift<br>modulation | All switches are driven by 50% of duty-cycle                                     | ZVS for primary<br>switches, ZCS for sec-<br>ondary switches                  | Narrow                      | Triple                   | Fast                                     | average                              |

| Series reso-<br>nant DAB          | Series reso-<br>nant tank      | Phase-shift<br>modulation | All switches are driven by 50% of duty-cycle                                     | ZVS for inverter<br>switches, ZCS for recti-<br>fier switches                 | Narrow                      | Double                   | Fast                                     | average                              |

| CLLC-DAB<br>symmetric<br>resonant | Series reso-<br>nant tank      | Frequency<br>modulation   | 50% of duty-cycle for in-<br>verter switches, turn off<br>for rectifier switches | ZVS for inverter<br>switches, soft commuta-<br>tion for rectifier<br>switches | Wide                        | Double                   | Slow                                     | high                                 |

Table 4 Comparison of various topologies operated with soft-switching. Conclusion based on [4]

### 2.2. Dual active bridge topology

In the present section, the configuration of the DAB converter and the basic principal operation will be discussed.

This topology for bidirectional isolated DC-DC converter was presented in 1991 [4] for highpower-density power converters. In the right side of the circuit, a battery pack is connected to the dc-dc converter. As discussed in topic 2.1.1 the main circuit consists of a two single-phase voltage source inverter connected by a high-frequency transformer that provides galvanic isolation. The link-inductor allows controlling the power flow in both directions between the battery and the DC-link that interfaces the inverter. Another feature of this topology is that the converter can also be operated in boost and buck mode. L represents the link-inductor and the  $V_{DC}$  is the voltage at the inverter, from the left side, that should be kept constant at the rated value. Figure 2.5 represents a simple DC-DC converter configuration, which is expected to be implemented with the elaboration of this dissertation.

Figure 2.5 - Single-phase dual active bridge topology for IBDC converter.

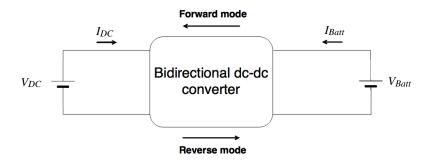

Two modes of operation with a soft-switching modulation can be defined:

- o Forward-mode: when the battery pack is discharging

- o Reverse mode: when the battery pack is charging

Figure 2.6 - Forward mode  $I_{Batt} > 0$  and  $I_{DC} < 0$ . Reverse mode  $I_{Batt} < 0$  and  $I_{DC} > 0$ .

Due to the considerable number of semiconductors in this topology, it is required implementation of strategies to reduce the commutation losses, namely the zero-voltage-switching (ZVS) and zero-current-switching (ZCS) technique. The ZVS allow to eliminate losses during turn ON transition, however the switching losses during turn OFF still be occurred on semiconductor switched [11], while ZCS is used to eliminate the losses when the switch turns OFF and reduce the losses when the switch turns ON.

The dual active bridge has advantages of "high power density, zero-voltage switching (ZVS), bidirectional power transfer capability, a modular and symmetric structure, and simple control requirements." [12].

The next section provides an overview of the main known modulation techniques. A detailed analysis for each of the control techniques will be presented.

#### 2.3. Modulations for the DAB

For the topologies previously presented, the implementation of a control method is a requirement to control the amount of energy circulating in both directions and that bidirectional flow of energy is achieved through modulation techniques. This section will introduce and analyze some of the most used modulation methods on dual active bridge topologies.

#### 2.3.1. Phase-shift modulation

The traditional and standard method for command the dual-active-bridge consists in control all transistors of both bridges through the single phase-shift. The diagonal transistors pairs are simultaneously switched with 50% of duty-cycle and the other complemented transistors in the same bridge with also 50% duty-cycle ratio but with 180 degrees of phase-shift. Providing a quasi-square waveform of high-frequency across the terminal of the external inductor *L* and the secondary transformer side. To control the power flow between two bridge/inverters, in other words, the direction and magnitude of current in the external inductor *L* is controlled by regulating the phase-shift ratio – *D* normalized - of two square waveforms,  $v_{pri} \in v_{sec}$ , generated by the respective bridges. The power flow is described by the following mathematical equation (2.1), first introduced in 1992 [13], and the losses are neglected:

$$P_{PSM} = \frac{NV_{Batt}V_{DC}}{8F_SL}D(2-|D|)$$

(2.1)

When D = 1, corresponding to the phase-shift maximum between the square voltage  $v_{pri}$ and  $v_{sec}$  possible in DAB under PSM to transfer power. In equation (2.1) the  $V_{DC}$  and  $V_{Batt}$  represent the amplitude of the primary and secondary voltage applied to both output sides of H-bridges respectively, wherein the DC-link bus is primary voltage and the battery side is the secondary voltage. The  $F_S$  is the frequency that transistors on inverters/bridge are commuted, the N is the transformer turns ratio and at last L could be the leakage inductance of the transformer, if the transformer is designed to have a desired leakage inductance to meet the requirements by applying the traditional phase-shift, or an external inductor. Considering the L an external inductor coupled to the primary of the transformer, this element is the most important parameter in power circuit for energy transfer, therefore its dimensioning is crucial to make converter operate in the desired power range. The L could also be represented by the sum of the external impedance and the intrinsic transformer leakage inductance. More later in Chapter 3 the converter design will be discussed.

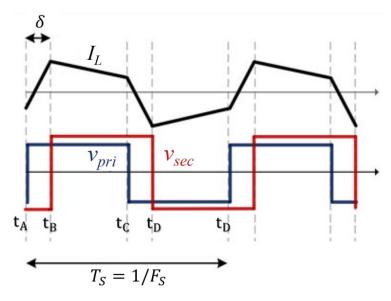

The single DAB is operated in a two-level waveform with the control technique presented in this topic. The resulted of single phase-shift is shown in Figure 2.7, adapted from [14], were the main ideal waveforms are presented.

Figure 2.7 - Idealized operating waveforms of the DAB converter  $(i_L, v_{pri} \text{ and } v_{pri})$ , and  $v_{pri}$  lead  $v_{sec}$ .

Where is observed in Figure 2.7 the voltage  $v_{pri}$  lead the voltage  $v_{sec}$  and the power flow from the DC-link side  $(V_{DC})$  to the battery side  $(V_{Batt})$ . When the  $v_{pri}$  is positive and the  $v_{sec}$ negative, between  $t_A$  and  $t_B$ , the  $i_L$  is increasing. During the next time segment  $t_B \le t \le t_C$  the current  $i_{lk}$  starts decreasing once the  $v_{sec}$  is higher than  $v_{pri}$ .

Figure 2.8 - Simplest diagram of power flow on DAB-IBDC converter with phase-shift modulation. Arrows indicate the direction of energy flow in the converter.

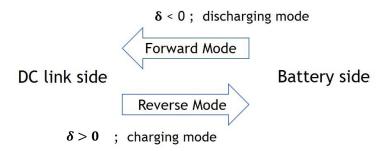

With the support of diagram from Figure 2.8, for the battery be in charging mode the phaseshift must be higher than zero, assume a positive value. In this scenario, the voltage  $v_{pri}$  lead behind  $v_{sec}$ . The battery is in discharging mode when phase-shift between primary voltage and secondary voltage of HF transformer is negative. Therefore,  $v_{pri}$  has a lag in relation to the  $v_{sec}$ . Summarily the power flow in dc-dc converter from the bridge with square voltage in the lead to the bridge with a square voltage in lag, in such way, the bidirectionality is achieved due to the phase-shift concept. The soft-switching is a technique commonly used in the DC-DC converter to make high efficiency resulting from the reduction of switching losses.

With this phase-shift modulation, the power flow through the leakage inductance depends on its value. There is a significant circulating power when the voltage amplitude of two sides of the transformer is not matched, then both the RMS and peak current increase. Moreover, the converter cannot operate under ZVS in the whole power range in this situation. Therefore, the power loss becomes much higher, and its efficiency is significantly reduced. [3].

# 2.3.2. Dual-phase-shift modulation

With the dual-phase-shift (DPS) technique there are two ways to control the power flow. The direction and magnitude of current are controlled by adjusting the phase-shift between transformer primary and secondary square voltage and also the phase-shift between the gate signals of the diagonal switches of each bridge. This control concept of dual phase-shift was presented in [15] with a two degree of freedom to control the system, one by adjusting the outer-phase-shift  $(D_2)$  between  $v_{pri}$  and  $v_{sec}$  that is the same parameter adjusted in traditional single phase-shift, and the other by shifting gate signals of diagonal semiconductors, e.g., introducing a phase-shift  $(D_1)$  between S1 and S4 gate signal in first H-bridge represented in Figure 2.5, also designed inner-phase-shift. The algorithm proposed for DPS can decrease peak current, reducing the losses and increasing the system efficiency. Also eliminates reactive power that circulates in the power transformer, increase power capability, and minimize the output capacitance [15].

Differently from the traditional two-level voltages at the secondary and primary output of the transformer, with the DPS control algorithm, the voltage emerges on three voltage levels, as we can be seen in Figure 2.9 ( $v_{pri}$  and  $v_{sec}$ ), from [16]. The approximated sinusoidal waveform of the current in the external inductor placed in the transformer primary side is one of the advantages of implementing the DPS with the consequent reduction of electromagnetic interference (EMI).

Figure 2.9 - (a) Ideal waveform of IBDC under DPS in the condition of  $0 \le D_1 \le D_2 \le 1$ . (b) Ideal waveforms of IBDC under DPS control in the condition of  $0 \le D_2 \le D_1 \le 1$  [16].

The output power analysis in the DAB converter with dual phase-shift modulation is expressed by the following equations [16, 17]:

$$0 \le D_1 \le D_2 \le 1 \qquad P_{DPS} = \frac{NV_{Batt}V_{DC}}{4F_SL} \times (2D_2 - 2D_2^2 - D_1^2) \qquad (2.2)$$

$$0 \le D_2 \le D_1 \le 1 \qquad P_{DPS} = \frac{NV_{Batt}V_{DC}}{4F_SL} \times (2D_2 - 2D_2D_1 - D_2^2)$$

(2.3)

## Some considerations:

- The primary or secondary square voltage,  $v_{pri}$  or  $v_{sec}$  respectively, not have necessarily the same duty-cycle e.g. constant 50% for one bridge and different ratio for the other bridge. The voltage waveform shown in Figure 2.9 with three-level is responsible for the significantly reduction of reactive power;

- $\circ$  All semiconductor switches are driven with 50% of duty cycle;

- The signal for the diagonal switches in both bridges has a phase-shift of  $D_1$ ;

- For the traditional phase-shift control only one degree of freedom is adjusted the phase shift between the primary and secondary voltage of both side of the transformer,  $v_{pri}$  and  $v_{sec}$  respectively;

- For the same output power there is an infinite combination of two-phase shift,  $D_1$ , and  $D_2$ ;

- From (2.2) and (2.3), the maximum output power in DPS cannot be concluded that is higher than SPS [17];

- "The DPS control can offer wider power transmission range than the SPS control does that will also enhance regulating flexibility" [16];

- "With the same current stress, the DPS control can transfer more power than the SPS control does" [16].

Figure 2.10 – Comparison of control algorithms SPS and DPS. (a) Transformer secondary voltage under SPS and DPS. (b) Primary current resulted by implements SPS and DPS under same output power. (c) Voltage ripple for two control algorithms (same PI parameter,  $C = 200\mu$ F) [15].

Figure 2.10 shows the simulation results of two different control algorithms (SPS and DPS) made by author [15], where the voltage waveform of the transformer secondary side are present

in Figure 2.10 (a). And in the Figure 2.10 (b) is shown the transformer current in the primary side for the two types of control modulation and following the converter topology of Figure 2.1. This result is obtained under the same output power. The output voltage ripple (DC-link side) in DAB converter for two control algorithms is shown in Figure 2.10 (c). With the same parameter of PI controller and the same output power, the author in observed that the peak current of DPS control is much smaller compared to the SPS control. The smaller voltage ripple observed in Figure 2.10 (c) results from the reduced inherent reactive power of using the DPS modulation in the DAB converter.

The authors in [15] also present a detailed analysis of soft-switching of the DPS control only for the operating mode  $D_1 \le D_2 \le (1 - D_1)$ , and it is verified that all the turn-off commutations occur with hard-switching, while zero-current-switching (ZCS) is implemented for all the turnon actions.

#### 2.3.3. Trapezoidal and triangular modulation

Due to the disadvantage of traditional SPS modulation, another advanced modulation was investigated to improve the efficiency of conversions, such as the triangular and trapezoidal modulation, TRM and TZM respectively.

## a) Trapezoidal modulation

Different from the conventional PSM, in TZM the duty cycle of the transformer output voltage waveforms, primary and secondary side, (converter topology of Figure 2.5), they are not driven by the same duty cycle. Where it can be seen in Figure 2.11, adapted from [18], the D11 and D12 can be less under 0.5 and also different from each other [18]. The  $D_{11}$  and  $D_{12}$  on equation (2.4) are the duty rate in p.u., where 1 p.u. represents 360° and when the  $D_{11}$  and  $D_{12}$  are equal 0.5 p.u., the DAB is modulated under SPS modulation, and the transformer voltage has a square waveform with 50% of the duty cycle and the transferred power is controlled by phaseshift  $\phi$ . In TZM the output power is described by the equation (2.4), adapted from [18]. To convert the phase shift in p.u. into to radians, can be easily made by multiplying it by  $2\pi$ .

$$P_{TZM} = \frac{V_{DC}}{LF_S} \left( D_{11}^2 V_{DC} - (D_{12} - \phi)^2 N V_{Batt} \right)$$

$$D_{12} = \frac{V_{DC}}{N V_{Batt}} D_{11}$$

(2.4)

The waveform of  $i_L$  in Figure 2.11 (a) can be observed in four different sequences of time. The transformer current encrease from zero between  $t_0 < t < t_1$ , in the next time segment  $t_1 < t_1$   $t < t_2$  the  $V_{DC}$  and  $NV_{Batt}$  is applied to the transformer. The indutor current decrease to zero between the segment  $t_2 < t < t_3$ , and reach the zero in  $t_4$ . At instant of time  $t_0$ ,  $t_4$ ,  $t_5$  and  $t_6$  the indutor current reaches the zero and ZCS is possible [19], therefore the ZCS occur in four transistor and ZVS for the others four, so the trapazoidal modulation has high efficiency inherent by the soft-switching implementation in some transistors, and also allow high power transfer.

Figure 2.11 - Ideal waveforms of the two different modulations and the power transit between first H-bridge into second H-bridge. (a) Trapezoidal modulation. (b) Triangular modulation.

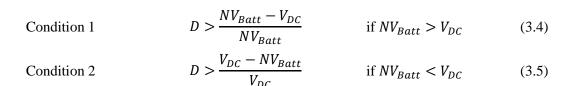

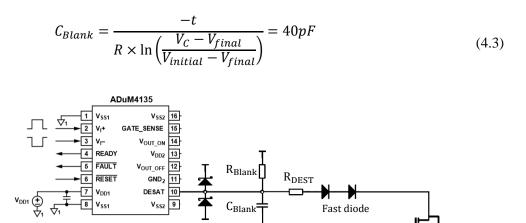

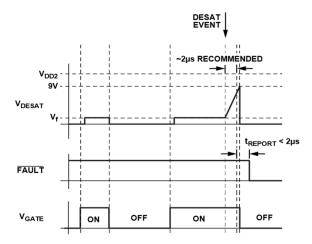

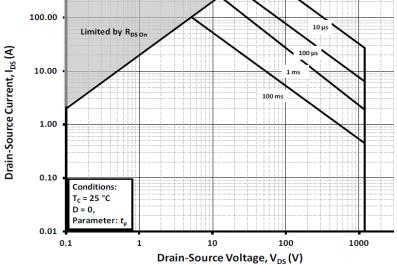

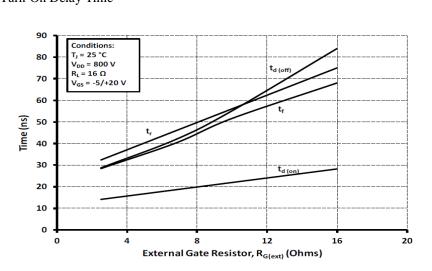

## b) Triangular modulation